## **Asynchrone Taktübergänge**

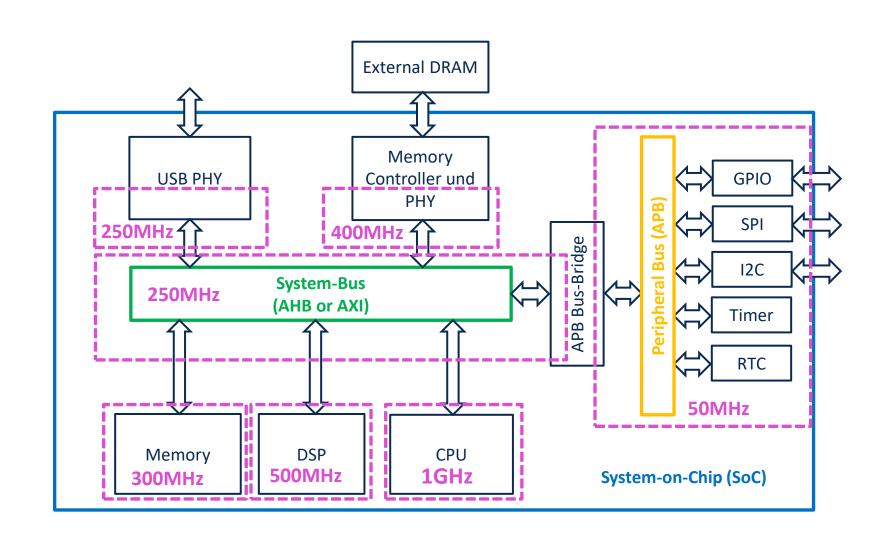

- Komplexe SoCs bestehen aus mehreren Takt-Domänen

- Separate Takterzeugung unterschiedlicher Taktfrequenzen für einzelne Systemkomponenten

- Separate Place&Route Makros mit unterschiedlichen Größen und unterschiedlichen Takt-Baum Tiefen

- Verschiedene Takt-Signale auf realisierten Takt-Bäumen (z.B. Mission-Mode Clk versus Scan Test Clock

- Herausforderungen:

- Timing Sign-off mit verschiedenen Takt-Domänen

- Datenübergänge zwischen verschiedenen Takt-Domänen

## Beispiel SoC mit mehreren Taktdomänen

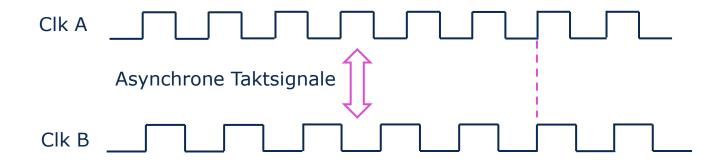

- Asynchrone Taktsignale:

- → unterschiedliche Frequenz und Phase

- Mesosynchrone Taktsignale:

- → gleiche Frequenz, unterschiedliche Phase

- Synchrones Daten Signal:

- "Launch" und "Capture" auf Flanken des selben Taktes

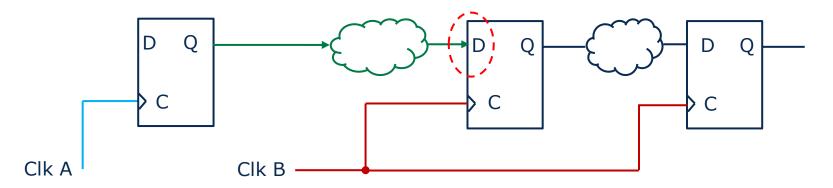

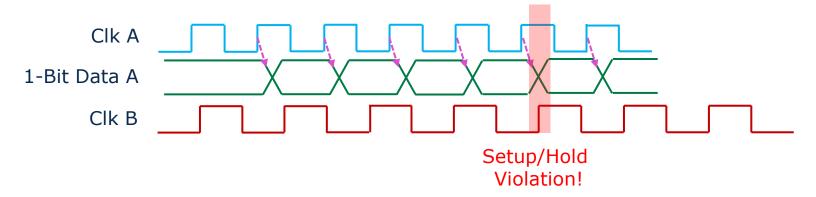

- Asynchrone Signale:

- "Launch" und "Capture" auf Flanken verschiedener asynchroner Takte

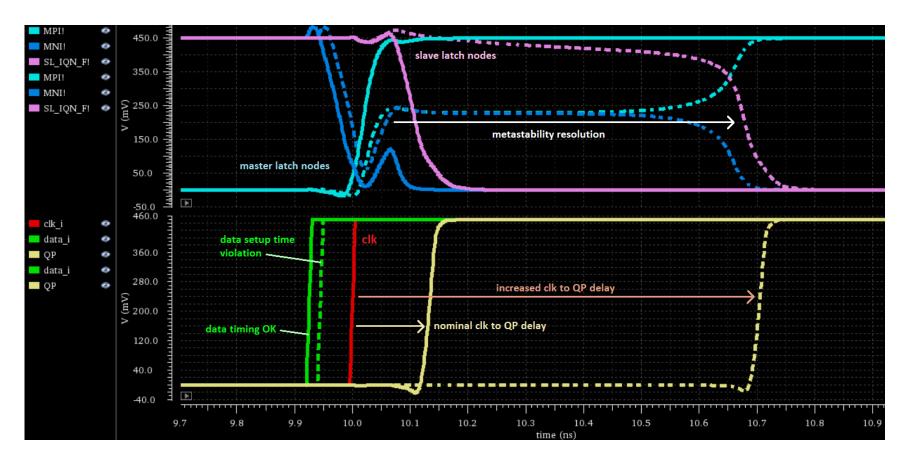

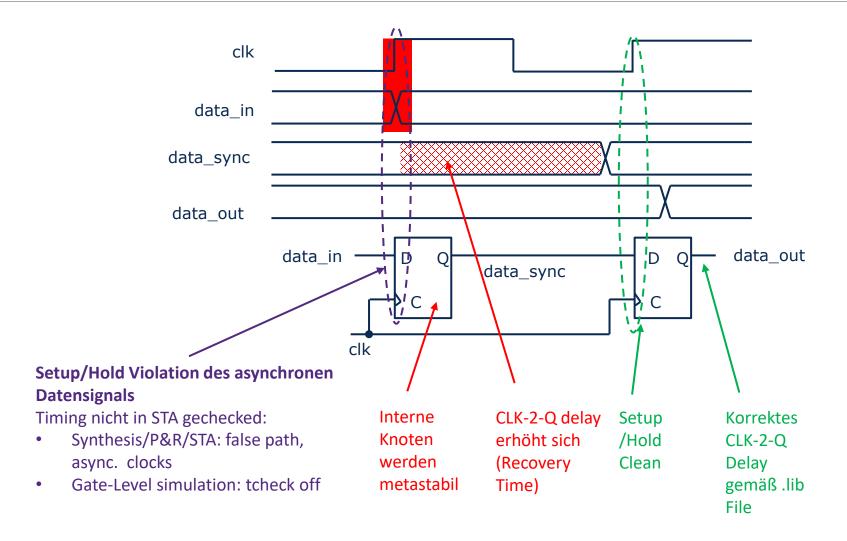

- Setup/Hold Violation können **Metastabilität** in FlipFlops/Latches verursachen

- Interne Speicherknoten verbleiben längere Zeit auf mittleren Signalpegeln (nicht stabil)

- Erhöhung der Clock-2-Q Delay Zeit des FlipFlops → mögliche weitere Timing Violations

## Metastability Mean Time to Failure

- Berechnung der Wahrscheinlichkeit, dass eine Metastability-bezogene Timing Violation auftritt.

- Mean-Time-To-Failure MTTF

- Definitionen:

- Zellen-spezifische Parameter:

- Tw Metastability Zeitfenster

- τ Latch interne Recovery Zeitkonstante

- tdi CLD-2-Q Delay des Master Latches im FlipFlop

- tdo Ausgangsdelay des FlipFlop

- ts Setup Zeit des FlipFlops

- System-spezifische Parameter:

- Tclk Clock period

- α Data toggle rate

Mean-time-to-failure:

$$\begin{aligned} \text{MTTF=1/}\alpha \cdot \text{Tclk}^2 \cdot \tau \cdot 1/\text{Tw}^2 \cdot e^{(\text{Tclk/2-tdi})/\tau} \cdot e^{(\text{Tclk/2-tdo-ts})/\tau} \\ &\quad \text{master latch} \quad \text{slave latch} \\ &\quad \text{recovery} \quad \end{aligned}$$

System MTTF:

- Beispiel: 2-Stage Synchronizer

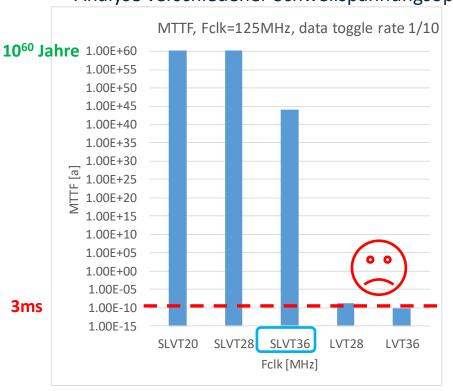

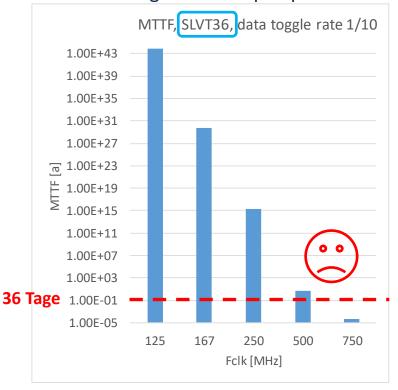

- Ultra-Low-Voltage Betrieb bei VDD=0.50V

- Analyse verschiedener Schwellspannungsoptionen und Gate-Längen L der FlipFlops

- Exponentielle Abhängigkeit der MTTF zur Vt-Option der FlipFlop Zellen

- → Synchronizer sollten kleine VT nutzen

- → Die Taktfrequenz des zu synchronisierenden Signals sollte minimiert werden

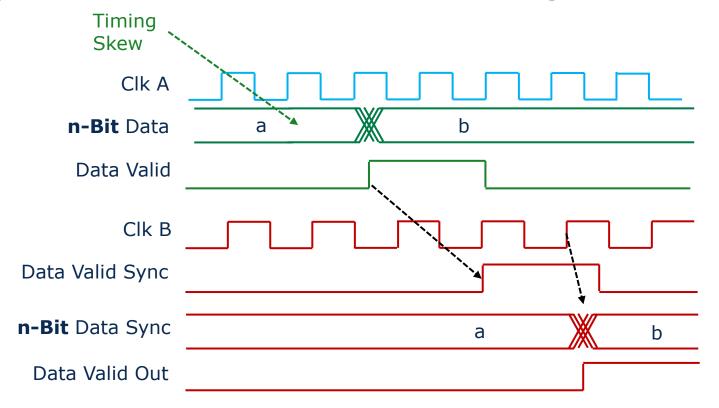

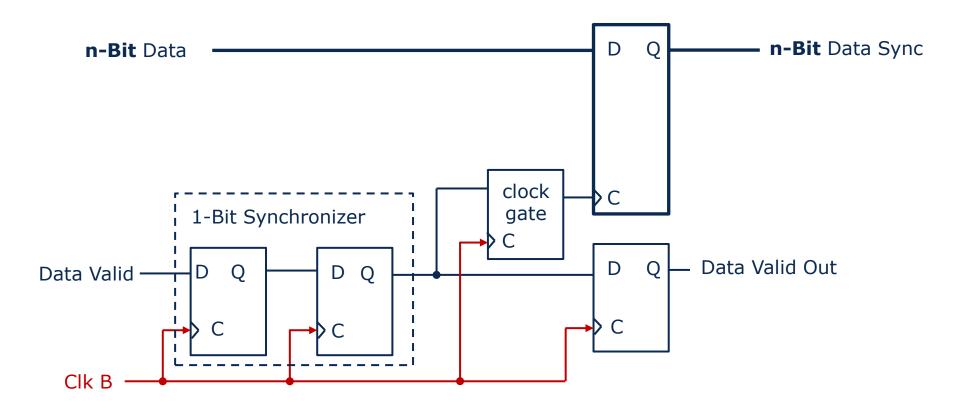

## Synchronisation von Multi-Bit-Signalen

- Wie synchronisiert man Multi-Bit Signale?

- Unterschiedliche Laufzeit der n Datenbits im Datenbus → Timing Skew

- n mal 1-Bit Synchronisation würde die Konsistenz der Daten zerstören

- → Synchronisation eines **zusätzlichen, 1-Bit Valid-Signals** in die Zieldomäne