The hyperlinks to the video streams in this virtual lecture are marked by the <u>Video Campus Sachsen Logo</u>. To watch them you <u>need to be logged</u> on at the host: <u>VCS</u>. Please click on: <u>https://videocampus.sachsen.de/login</u> <u>select TU-Dresden</u> in the selection mask and than logon with the same ID and password as you use for OPAL or ZIH. Stay logged on as long as you work with the lecture slides.

# Lecture SCT2 - Process Integration

#### 4. Web-based virtual Lecture: May 06 2021 Prof. Dr. Johann W. Bartha

Inst. f. Halbleiter und Mikrosystemtechnik Technische Universität Dresden

Summer Semester 2021

"SCT\_SS21\_04.1" 14:20

This document including the contained video streams is only available to students of the lecture "Semiconductor Technology 2" at TU-Dresden. It must not be copied and published outside of TUD! It is intended for TUD internal use only!

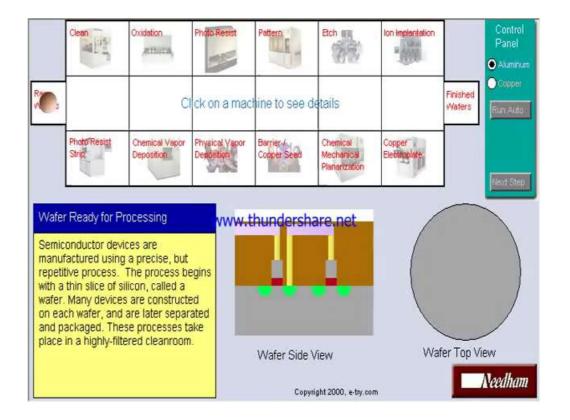

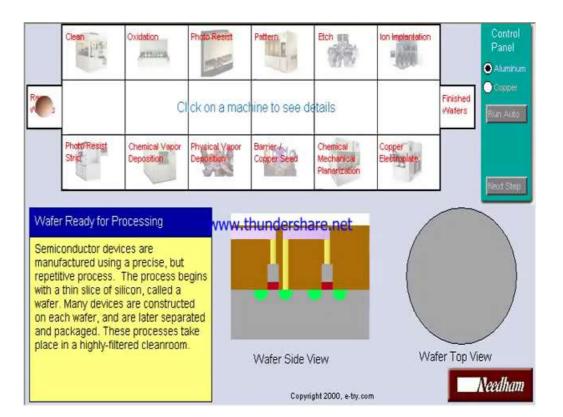

### Generic simulation of a MOS FET process flow

### Generic simulation of a MOS FET process flow

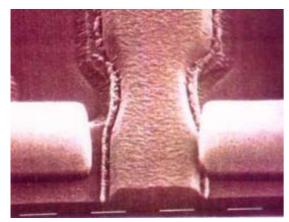

## DRAM Polycide RIE

Dresden Microelectronics Academy

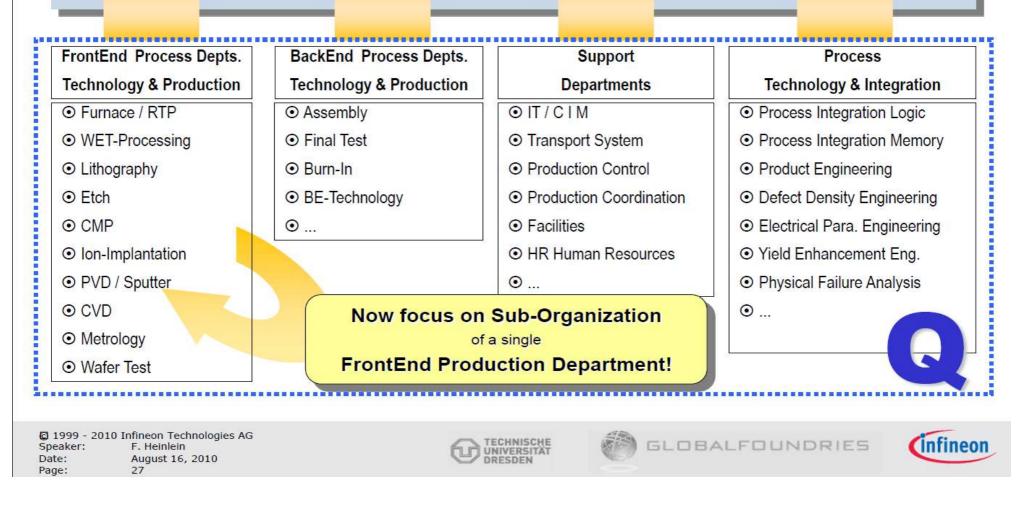

#### A Production Organization Typical Departments

## PRODUCTION

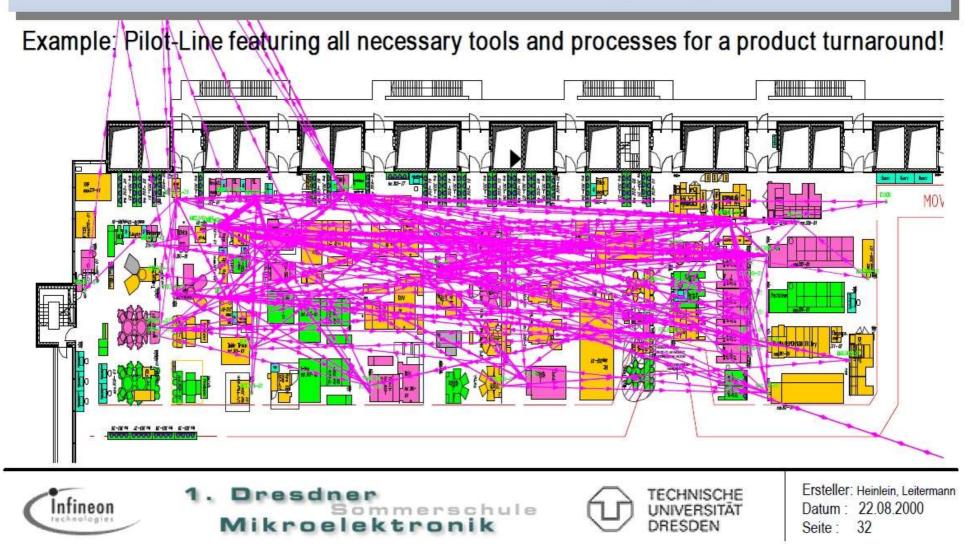

#### Illustration of Production Complexity

| ine | 0. Introduction/Lab organization/DMA/SCT1/Motivation | SC-<br>Basics |

|-----|------------------------------------------------------|---------------|

|     | 1. Process integration                               |               |

|     | 1.MOS Structure, MOS Capacitor                       | Basics        |

|     | 2.Structure of a MOSFET                              |               |

|     | 3.I/V behaviour                                      |               |

|     | 2. Circuits in Metal-Gate FET Technology             |               |

|     | 1. Process sequence of N-MOSFET in Metal Gate        |               |

|     | 2.From inverter to memory cell                       |               |

|     | 3.SRAM in NMOS Metal Gate                            |               |

|     | 4. The threshold voltage of the MOSFET               |               |

|     | 1.Parasitic FET                                      |               |

|     | 2.Enhancement/Depletion Transistor                   |               |

|     | 3.N-MOS Logic by E/D Transitors                      |               |

|     | 4. Process sequence of the N-MOS E/D Process         |               |

|     | 3. Self aligned Process                              |               |

|     | 1.Metal Gate -> Si Gate                              |               |

|     | 2. Channel-Stop & LOCOS Technology                   |               |

|     | 1.Example: Process flow of E/D SiGate LOCOS Inve     | rter          |

|     | 2.LOCOS Variation                                    |               |

|     | 3.Shallow Trench Isolation                           |               |

|     | 3.Lightly doped drain<br>4.SALICIDE                  |               |

|     | 5. Self Aligned Contacts (SAC)                       |               |

|     | 6. Resist trimming                                   |               |

|     | 4. Transition to CMOS Technology                     |               |

|     | 1.MOS Transistor Types                               |               |

|     | 2.CMOS Inverter                                      |               |

|     | 1.Consideration NMOS E/D Inverter                    |               |

|     | 2.Comparison CMOS Inverter                           |               |

|     | 3.CMOS Process flow (Example CMOS 180 nm process)    |               |

|     | 5. Further Considerations                            |               |

|     | 1.Scaling                                            |               |

|     | 1. Challenges                                        |               |

|     | 2.Material Equivalent Scaling                        |               |

|     | 3.Further Concepts                                   |               |

http://www.computerhistory.org/siliconengine/timeline/

| 0. Introduction/Lab organization/DMA/SCT1/Motivation | SC- Basics |

|------------------------------------------------------|------------|

| 1. Process integration                               | Design     |

| 1.MOS Structure, MOS Capacitor                       | Basics     |

| 2.Structure of a MOSFET                              |            |

| 3.I/V behaviour                                      |            |

| 2. Circuits in Metal-Gate FET Technology             |            |

| 1.Process sequence of N-MOSFET in Metal Gate         |            |

| 2.From inverter to memory cell                       |            |

| 3.SRAM in NMOS Metal Gate                            |            |

| 4. The threshold voltage of the MOSFET               |            |

| 1.Parasitic FET                                      |            |

| 2.Enhancement/Depletion Transistor                   |            |

| 3.N-MOS Logic by E/D Transitors                      |            |

| 4. Process sequence of the N-MOS E/D Process         |            |

| 3. Self aligned Process<br>1.Metal Gate -> Si Gate   |            |

| 2. Channel-Stop & LOCOS Technology                   |            |

| 1.Example: Process flow of E/D SiGate LOCOS Inv      | verter     |

| 2.LOCOS Variation                                    |            |

| 3.Shallow Trench Isolation                           |            |

| 3.Lightly doped drain                                |            |

| 4.SALICIDE                                           |            |

| 5. Self Aligned Contacts (SAC)                       |            |

| 6. Resist trimming                                   |            |

| 4. Transition to CMOS Technology                     |            |

| 1.MOS Transistor Types                               |            |

| 2.CMOS Inverter                                      |            |

| 1.Consideration NMOS E/D Inverter                    |            |

| 2.Comparison CMOS Inverter                           |            |

| 3.CMOS Process flow (Example CMOS 180 nm process)    |            |

| 5. Further Considerations                            |            |

| 1.Scaling                                            |            |

| 1. Challenges                                        |            |

| 2.Material Equivalent Scaling                        |            |

| 3.Further Concepts                                   |            |

http://www.computerhistory.org/siliconengine/timeline/

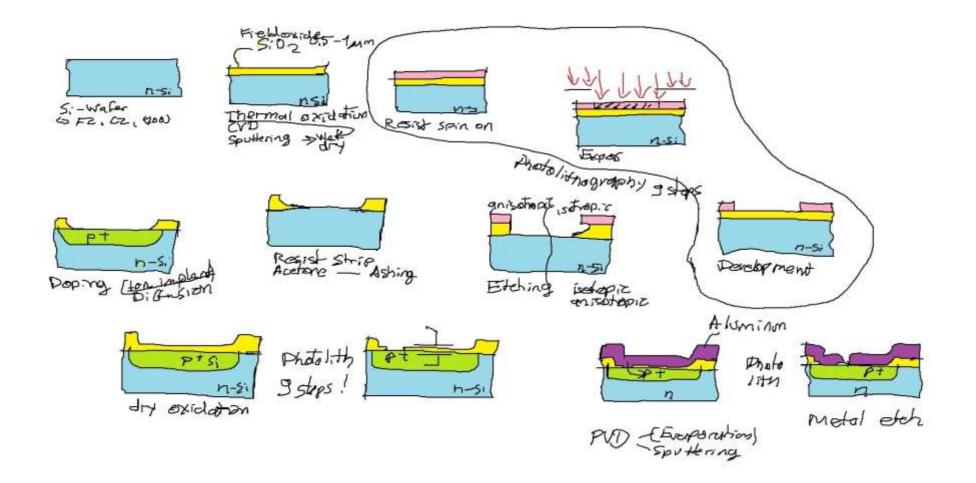

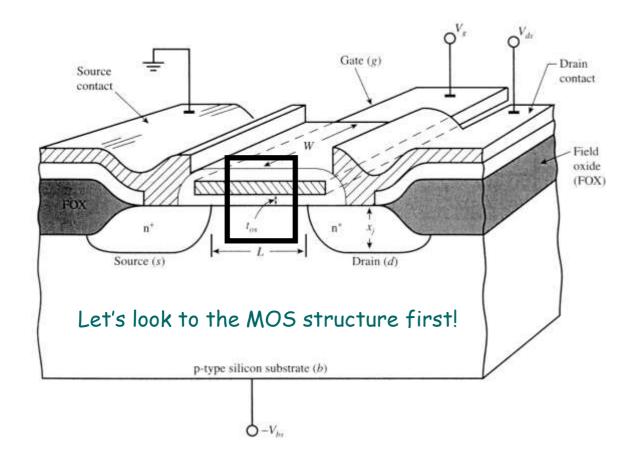

#### 1.1 MOS Structure - MOS Capacitor

#### 1.1 MOS Structure - MOS Capacitor

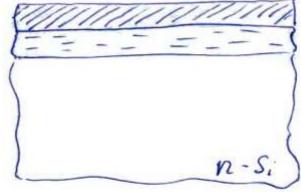

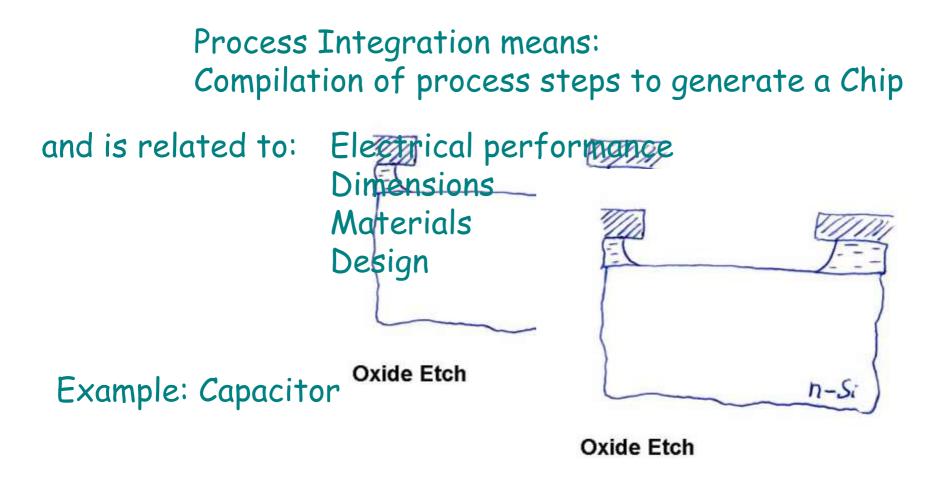

and is related to: Electrical performance Dimensions Materials Design

#### and is related to: Electrical performance Dimensions Materials Design

Example: Capacitor

Page: 13 LO4 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

### and is related to: Electrical performance Dimensions Materials Design

Example: Capacitor

Si Substrat

Page: 14 L04 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

### and is related to: Electrical performance Dimensions Materials Design

Example: Capacitor

**Resist Apply**

## and is related to: Electrical performance Dimensions Materials Design

Example: Capacitor

Expose

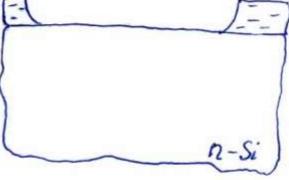

n-Si

Page: 16 L04 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

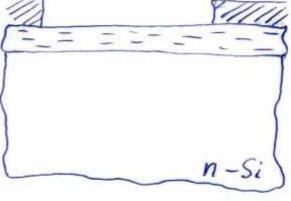

#### and is related to: Electrical performance Dimensions Materials Design

Example: Capacitor

Develop

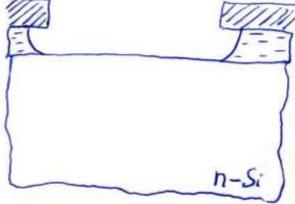

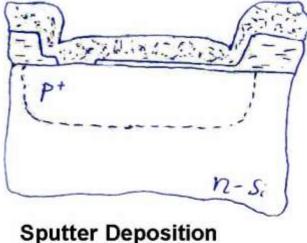

#### and is related to: Electrical performance Dimensions Materials Design

Example: Capacitor

**Oxide Etch**

and is related to: Electrical performance Dimensions Materials Design

Example: Capacitor

**Resist Strip**

#### and is related to: Electrical performance Dimensions Materials Design

Example: Capacitor

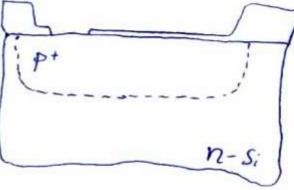

**Diffusion or Implant**

#### and is related to: Electrical performance Dimensions Materials Design

Example: Capacitor

**Dry Oxidation**

#### and is related to: Electrical performance Dimensions Materials Design

Example: Capacitor

Litho and Etch Oxide

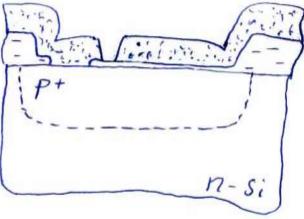

#### and is related to: Electrical performance Dimensions Materials Design

Example: Capacitor

## and is related to: Electrical performance Dimensions

Materials Design

Example: Capacitor

Litho and Etch Metal

#### and is related to: Electrical performance Dimensions Materials Design

Example: Capacitor

**Oxide Etch**

#### and is related to: Electrical performance Dimensions Materials Design

Example: Capacitor

Litho and Etch Metal

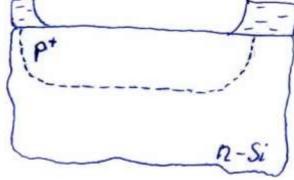

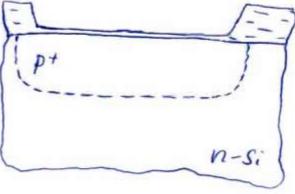

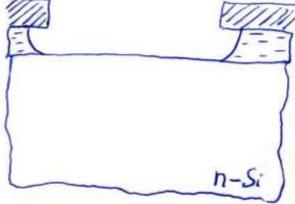

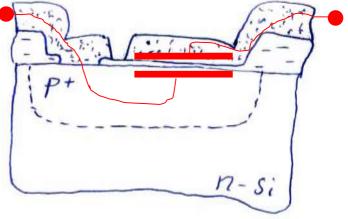

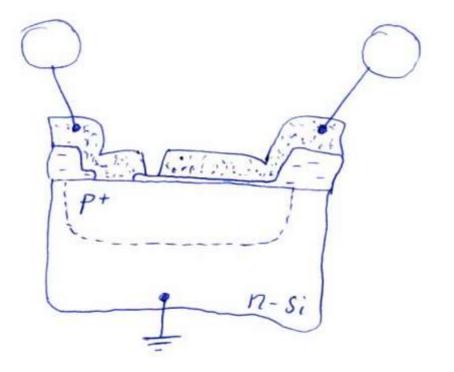

Question: If the substrate is grounded, is there a certain polarity required?

Question: If the substrate is grounded, is there a certain polarity required?

Question: If the substrate is grounded, is there a certain polarity required?

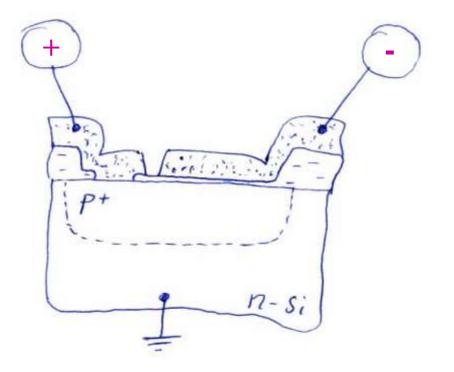

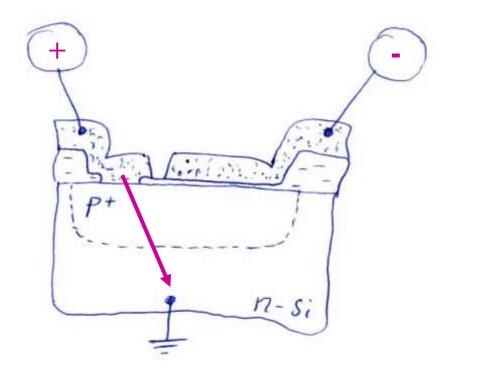

If the p+ terminal is connected to + we have a short to ground through the p<sup>+</sup>/n substrate diode

Question: If the substrate is grounded, is there a certain polarity required?

The substrate contact has to be minus otherwise the p<sup>+</sup>/n junction is in forward direction! If the p+ terminal is connected to + we have a short to ground through the p<sup>+</sup>/n substrate diode

Impact of material and layout:

Typical DRAM capacitor C = 30 fF  $C = Q/U; C = \varepsilon_0 \varepsilon_r A/d; \ \varepsilon_0 = 8.85 \ 10^{-12} F/m \\ \varepsilon_r(SiO_2) = 3.9$

Impact of material and layout:

Typical DRAM capacitor C = 30 fF

C = Q/U;  $C = \varepsilon_0 \varepsilon_r A/d$ ;  $\varepsilon_0 = 8.85 \ 10^{-12} F/m$  $\varepsilon_r(SiO_2) = 3.9$

charges at U = 2.5 V:  $Q = C \cdot U = 30 \cdot 10^{-15} F \cdot 2.5 V = 75 \cdot 10^{-15} As$  $(e = 1.6 \cdot 10^{-19} C)$  or 469000 Electrons ( Noise)

Impact of material and layout:

Typical DRAM capacitor C = 30 fF

$C = Q/U; C = \varepsilon_0 \varepsilon_r A/d; \varepsilon_0 = 8.85 \ 10^{-12} F/m \\ \varepsilon_r(SiO_2) = 3.9$

charges at U = 2.5 V:  $Q = C \cdot U = 30 \cdot 10^{-15} \text{ F} \cdot 2.5 \text{ V} = 75 \cdot 10^{-15} \text{ As}$ (e = 1.6 · 10<sup>-19</sup> C) or 469000 Electrons (> Noise)

Can this be realized with a cell size of  $1\mu m^2$ ?

Impact of material and layout:

Typical DRAM capacitor C = 30 fF

$C = Q/U; C = \varepsilon_0 \varepsilon_r A/d; \varepsilon_0 = 8.85 \ 10^{-12} F/m \\ \varepsilon_r(SiO_2) = 3.9$

charges at U = 2.5 V:  $Q = C \cdot U = 30 \cdot 10^{-15} \text{ F} \cdot 2.5 \text{ V} = 75 \cdot 10^{-15} \text{ As}$ (e = 1.6 \cdot 10^{-19} C) or 469000 Electrons ( Noise)

Can this be realized with a cell size of  $1\mu m^2$ ? Required oxide thickness: d =  $\varepsilon_0 \varepsilon_r A/C = 1.1 nm$

Impact of material and layout:

Typical DRAM capacitor C = 30 fF

$C = Q/U; C = \varepsilon_0 \varepsilon_r A/d; \ \varepsilon_0 = 8.85 \ 10^{-12} F/m \\ \varepsilon_r(SiO_2) = 3.9$

charges at U = 2.5 V:  $Q = C \cdot U = 30 \cdot 10^{-15} \text{ F} \cdot 2.5 \text{ V} = 75 \cdot 10^{-15} \text{ As}$ (e = 1.6 \cdot 10^{-19} C) or 469000 Electrons ( $\textcircled{\baselineskip}$  Noise)

Can this be realized with a cell size of  $1\mu m^2$ ? Required oxide thickness:  $d = \epsilon_0 \epsilon_r A/C = 1.1 nm$

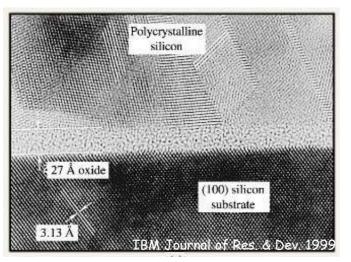

(Break Down Voltage of SiO<sub>2</sub> is 7 MV/cm, Further problem - tunnel current!) U/d = 2.5V/1.1 nm = 22 MV/cm !! Therefore minimum oxide thickness d = 3.3 nm This requires A = 3  $\mu$ m<sup>2</sup> or a different dielectric material (for example high k)!

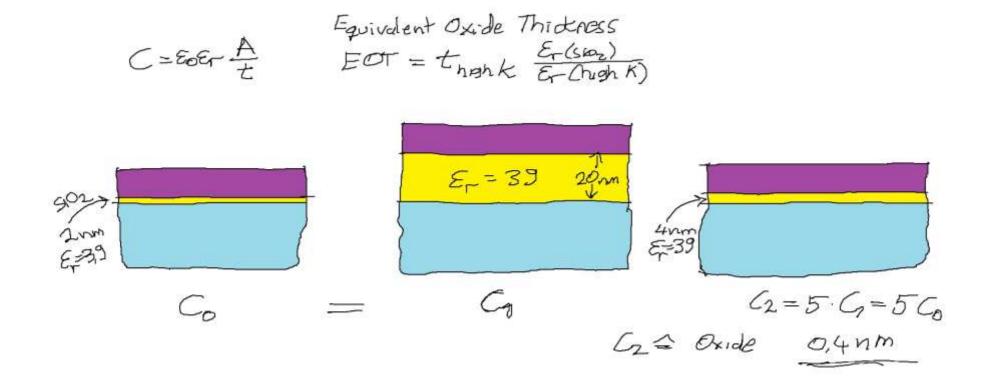

### High K - EOT

#### Equivalent oxide thickness

From Wikipedia, the free encyclopedia

An **Equivalent oxide thickness** is a distance, usually given in nanometers (nm), which indicates how thick a silicon oxide film would need to be to produce the same effect as the high-k material being used.

The term is often used when describing field effect transistors which rely on an electrically insulating pad of material between a gate and a doped semiconducting region. Device performance has typically been improved by reducing the thickness of a silicon oxide insulating pad. As the thickness approached 5–10 nm, leakage became a problem and alternate materials were necessary to increase the thickness while retaining the switching speed. Materials having larger dielectric constants enable thicker films to be used for this purpose while retaining fast reaction of the transistor. For example, a high- $\kappa$  material with dielectric constant of 39 (compared to 3.9 for silicon oxide) can be made ten times thicker than silicon oxide which helps to reduce the leakage of electrons across the dielectric pad, while achieving the same capacitance. Commonly used high- $\kappa$  gate dielectrics include hafnium oxide and more recently aluminum oxide for gate-all-around devices.

$$\mathrm{EOT} = t_{\mathrm{high} extsf{-}\kappa} \left(rac{k_{\mathrm{SiO}_2}}{k_{\mathrm{high} extsf{-}\kappa}}

ight).$$

The EOT definition is useful to quickly compare different dielectric materials to the industry standard silicon oxide dielectric, as:

$$\epsilon_0 \, \epsilon_{\mathrm{SiO}_2} rac{A}{\mathrm{EOT}} = \epsilon_0 \, \epsilon_{\mathrm{high} extsf{-}\kappa} \, rac{A}{t_{\mathrm{high} extsf{-}\kappa}} = C$$

#### Equivalent oxide thickness

From Wikipedia, the free encyclopedia

An **Equivalent oxide thickness** is a distance, usually given in nanometers (nm), which indicates how thick a silicon oxide film would need to be to produce the same effect as the high- $\kappa$  material being used.

The term is often used when describing field effect transistors which rely on an electrically insulating pad of material between a gate and a doped semiconducting region. Device performance has typically been improved by reducing the thickness of a silicon oxide insulating pad. As the thickness approached 5–10 nm, leakage became a problem and alternate materials were necessary to increase the thickness while retaining the switching speed. Materials having larger dielectric constants enable thicker films to be used for this purpose while retaining fast reaction of the transistor. For example, a high-k material with dielectric constant of 39 (compared to 3.9 for silicon oxide) can be made ten times thicker than silicon oxide which helps to reduce the leakage of electrons across the dielectric pad, while achieving the same capacitance. Commonly used high-k gate dielectrics include hafnium oxide and more recently aluminum oxide for gate-all-around devices.

$$\mathrm{EOT} = t_{\mathrm{high} extsf{-}\kappa} \left(rac{k_{\mathrm{SiO}_2}}{k_{\mathrm{high} extsf{-}\kappa}}

ight)$$

The EOT definition is useful to quickly compare different dielectric materials to the industry standard silicon oxide dielectric, as:

$$\epsilon_0 \ \epsilon_{\mathrm{SiO}_2} rac{A}{\mathrm{EOT}} = \epsilon_0 \ \epsilon_{\mathrm{high} extsf{-}\kappa} \ rac{A}{t_{\mathrm{high} extsf{-}\kappa}} = C$$

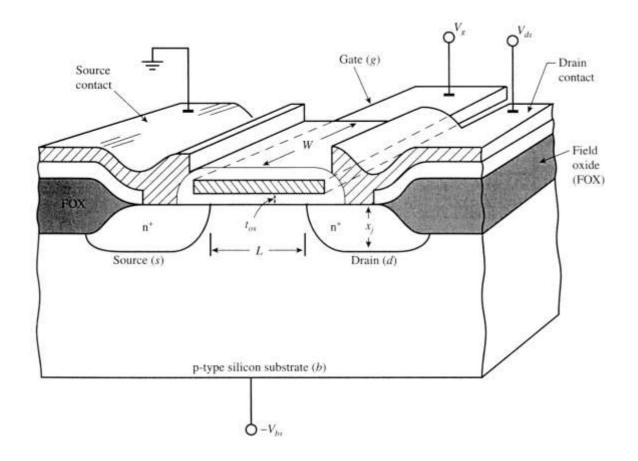

#### 1.2 Transition to the MOSFET

MOS capacitor CV behavior -Accumulation -Depletion -Inversion

#### 1.2 Transition to the MOSFET

MOS capacitor CV behavior -Accumulation -Depletion -Inversion

## »Wissen schafft Brücken.«

Page: 42 LO4 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!