The hyperlinks to the video streams in this virtual lecture are marked by the <u>Video Campus Sachsen Logo</u>. To watch them you <u>need to be logged</u> on at the host: <u>VCS</u>. Please click on: <u>https://videocampus.sachsen.de/login</u> <u>select TU-Dresden</u> in the selection mask and than logon with the same ID and password as you use for OPAL or ZIH. Stay logged on as long as you work with the lecture slides.

# Lecture SCT2 - Process Integration

### 10. Web-based virtual Lecture: June 24 2021 Prof. Dr. Johann W. Bartha

Inst. f. Halbleiter und Mikrosystemtechnik Technische Universität Dresden

Summer Semester 2021

Start lecture here

"SCT\_SS21\_10.1" 18:13

This document including the contained video streams is only available to students of the lecture "Semiconductor Technology 2" at TU-Dresden. It must not be copied and published outside of TUD! It is intended for TUD internal use only!

- SCT Basics

- MOS-Cap-CV

- MOS-FET

- Al-Gate FET

- SRAM production

- $V_T$  dependencies

- E/D Logic

- Si Gate

### Today: Further self alignment

SC-0. Introduction/Lab organization/DMA/SCT1/Motivation 1. Process integration Basics 1.MOS Structure, MOS Capacitor 2.Structure of a MOSFET 3.I/V behavior 2. Circuits in Metal-Gate FET Technology 1. Process sequence of N-MOSFET in Metal Gate 2.From inverter to memory cell 3.SRAM in NMOS Metal Gate 4. The threshold voltage of the MOSFET **1.Parasitic FET** 2.Enhancement/Depletion Transistor 3.N-MOS Logic by E/D Transitors 4. Process sequence of the N-MOS E/D Process 3. Self aligned Process 1.Metal Gate -> Si Gate 2. Channel-Stop & LOCOS Technology 1.Example: Process flow of E/D SiGate LOCOS Inverter 21.0COS Variation **3.Shallow Trench Isolation** 3. Lightly doped drain 4.SALICIDE 5. Self Aligned Contacts (SAC) 6. Resist trimming 4. Transition to CMOS Technology **1.MOS** Transistor Types 2.CMOS Inverter 1. Consideration NMOS E/D Inverter 2. Comparison CMOS Inverter 3.CMOS Process flow (Example CMOS 180 nm process) 5. Further Considerations 1.Scaling 1. Challenges 2. Material Equivalent Scaling 3. Further Concepts

- Si Gate

### Today: Further self alignment

SC-0. Introduction/Lab organization/DMA/SCT1/Motivation Basics 1.MOS Structure, MOS Capacitor 2. Circuits in Metal-Gate FET Technology 1. Process sequence of N-MOSFET in Metal Gate 2.From inverter to memory cell 4. The threshold voltage of the MOSFET 2.Enhancement/Depletion Transistor 3.N-MOS Logic by E/D Transitors 4. Process sequence of the N-MOS E/D Process 2. Channel-Stop & LOCOS Technology 1.Example: Process flow of E/D SiGate LOCOS Inverter **3.Shallow Trench Isolation** 3. Lightly doped drain **4.SALICIDE** 5. Self Aligned Contacts (SAC) 6. Resist trimming 4. Transition to CMOS Technology **1.MOS** Transistor Types 2.CMOS Inverter 1. Consideration NMOS E/D Inverter 2. Comparison CMOS Inverter 3.CMOS Process flow (Example CMOS 180 nm process) 5. Further Considerations 1.Scaling 1. Challenges 2. Material Equivalent Scaling 3. Further Concepts

Page: 4 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

http://www.computerhistory.org/siliconengine/timeline/

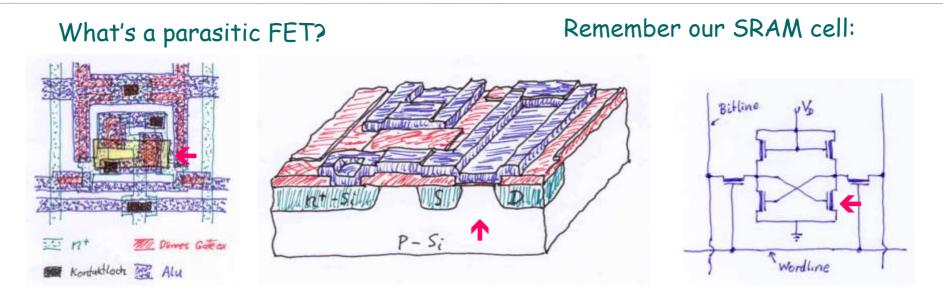

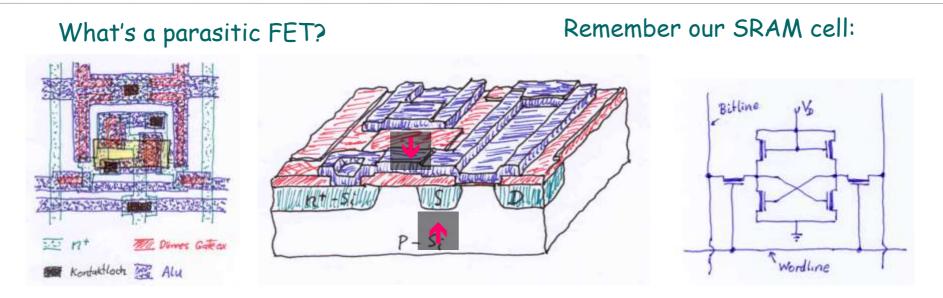

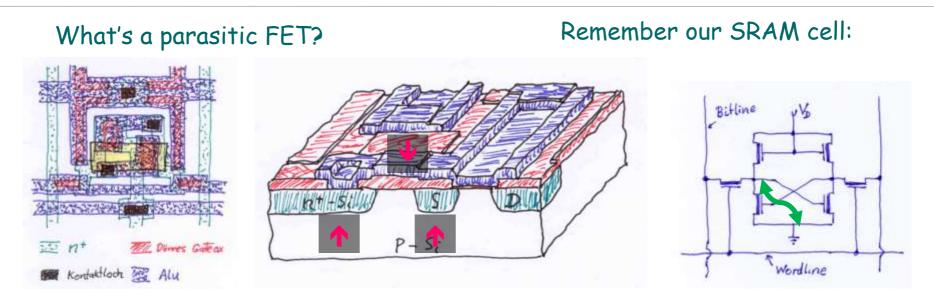

#### What's a parasitic FET?

#### What's a parasitic FET?

#### Remember our SRAM cell:

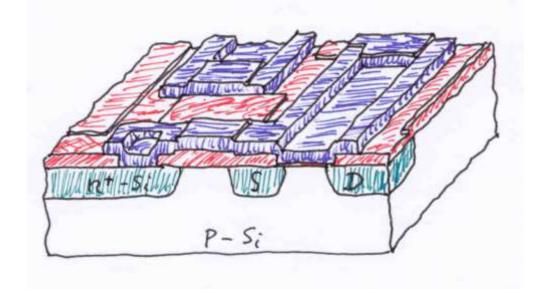

A regular FET is the switching transistor shown in the different pictures and consist of the n<sup>+</sup> Source, the p-substrate and the n<sup>+</sup> Drain region, the substrate region is covered with the thin oxide and the gate electrode.

Page: 7 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

The Gate-line runs over the fieldox to the left and connects to the Drain of the left switching transitor resp. the Source of the left load transistor.

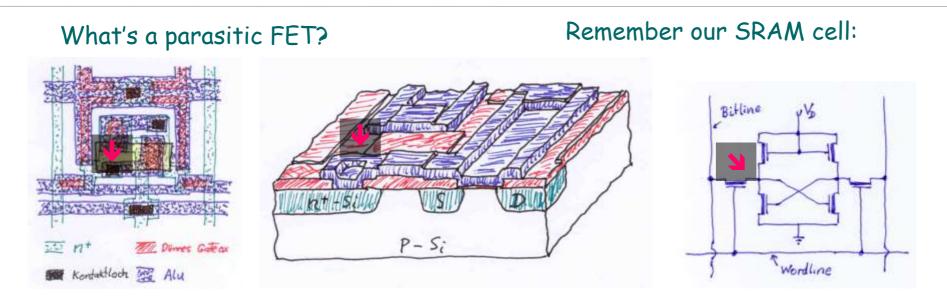

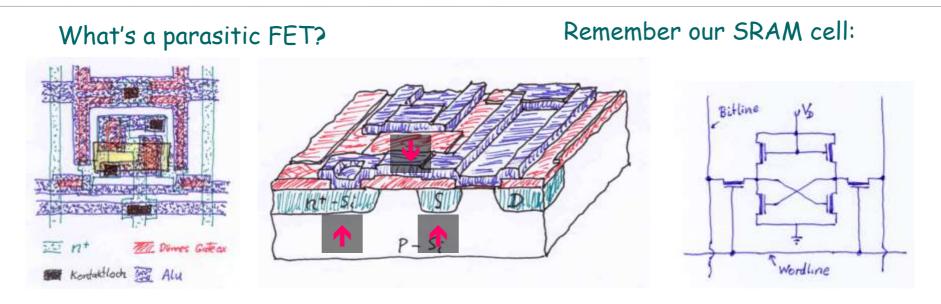

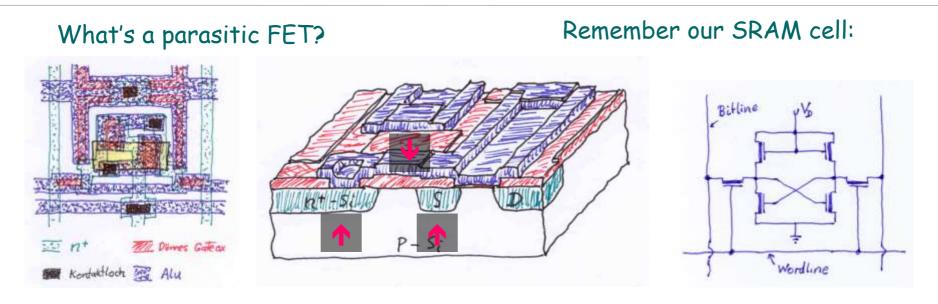

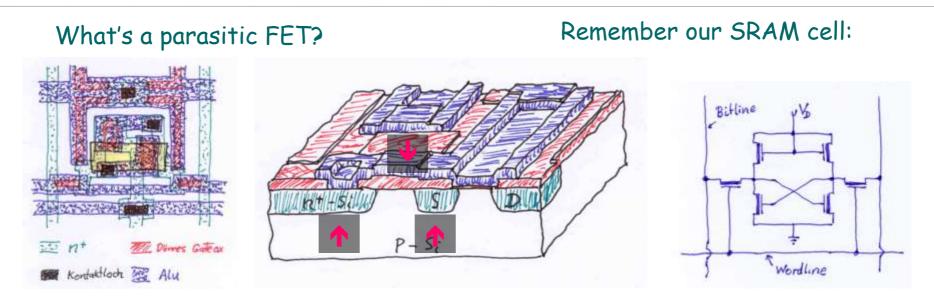

#### We can think of the source,

Page: 9 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

#### We can think of the source, the Gate over the fieldox,

Page: 10 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

#### We can think of the source, the Gate over the fieldox, and the n<sup>+</sup> line

Page: 11 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

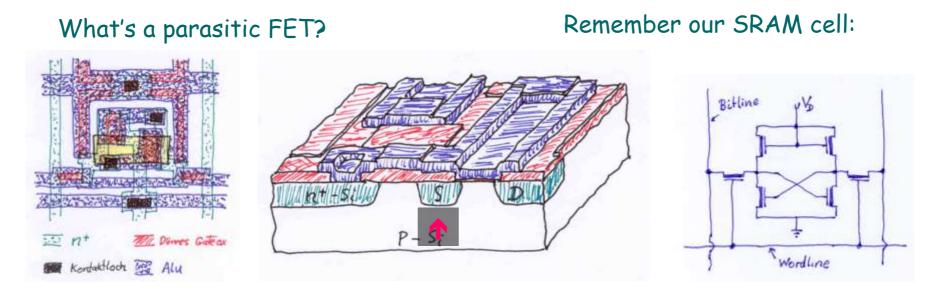

We can think of the source, the Gate over the fieldox, and the n<sup>+</sup> line as a further MOS FET, which has a high threshold voltage due to the large thickness of the fieldox.

Page: 12 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

We can think of the source, the Gate over the fieldox, and the n<sup>+</sup> line as a further MOS FET, which has a high threshold voltage due to the large thickness of the fieldox.

This FET is called parasitic transistor. It might unintentionally connect any n<sup>+</sup> region where Gate lines run over the fieldox. To avoid this, the fieldox thickness has to be as large as possible.

We can think of the source, the Gate over the fieldox, and the n<sup>+</sup> line as a further MOS FET, which has a high threshold voltage due to the large thickness of the fieldox.

This FET is called parasitic transistor. It might unintentionally connect any n<sup>+</sup> region where Gate lines run over the fieldox. To avoid this, the fieldox thickness has to be as large as possible.

We can think of the source, the Gate over the fieldox, and the n<sup>+</sup> line as a further MOS FET, which has a high threshold voltage due to the large thickness of the fieldox.

This FET is called parasitic transistor. It might unintentionally connect any n<sup>+</sup> region where Gate lines run over the fieldox. To avoid this, the fieldox thickness has to be as large as possible.

$$V_T = \frac{d_{ox}}{\varepsilon_{ox}} \sqrt{2\varepsilon_{Si}eN_A(2\Phi_F + V_{SB})} + 2\Phi_F - \frac{Q_{eff}}{C_{ox}} + \frac{\Delta W_F}{e}$$

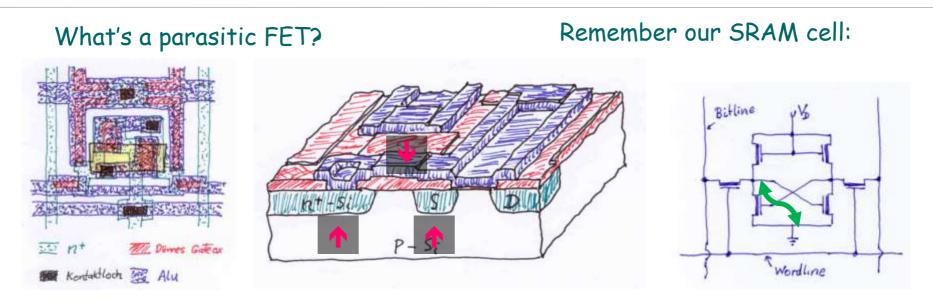

# Challenges associated with large d<sub>fox</sub> (field oxide thickness)

- Lithography on large topography CD=k<sub>1</sub>  $\lambda$ /NA and DOF=k<sub>2</sub>  $\lambda$ /NA<sup>2</sup>

berfocal distance opposite are using. If you the the depth of field with the to infinity.⊲ For amera has a hyperfor

Page: 16 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

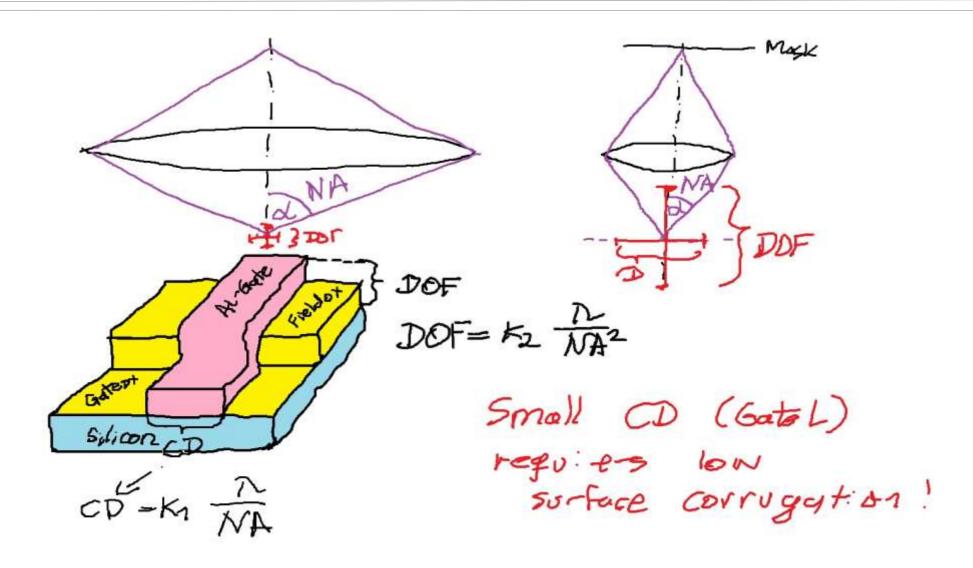

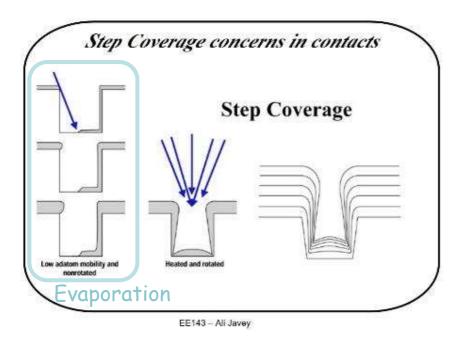

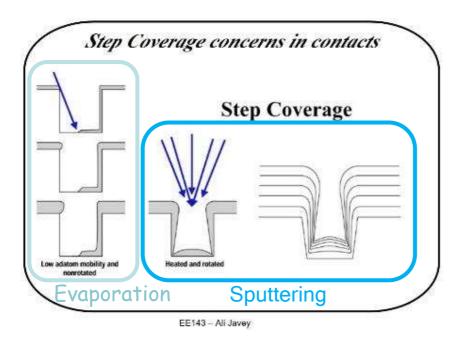

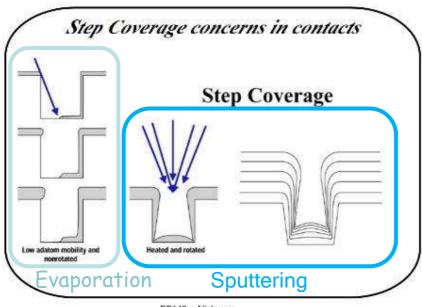

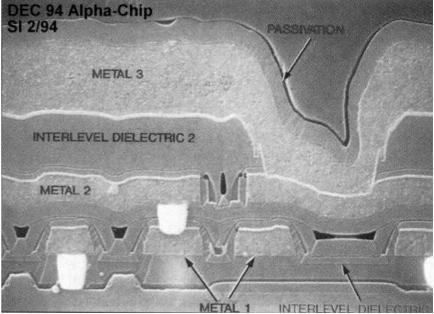

## Challenges associated with large $d_{fox}$ (field oxide thickness)

- Lithography on large topography CD=k<sub>1</sub>  $\lambda$ /NA and DOF=k<sub>2</sub>  $\lambda$ /NA<sup>2</sup>

- Step coverage of the metal layer

Page: 18 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

### + Inherent Uniformity Issues!

Page: 19 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

### + Inherent Uniformity Issues!

Page: 20 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

### + Inherent Uniformity Issues!

Page: 21 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

EE143 - Ali Javey

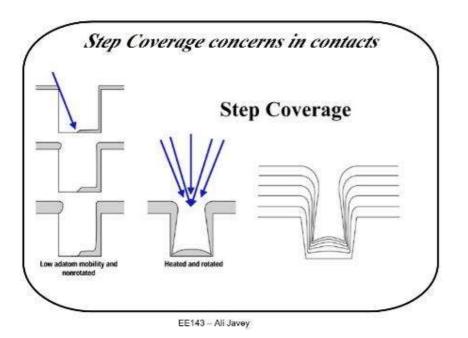

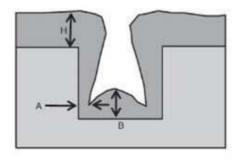

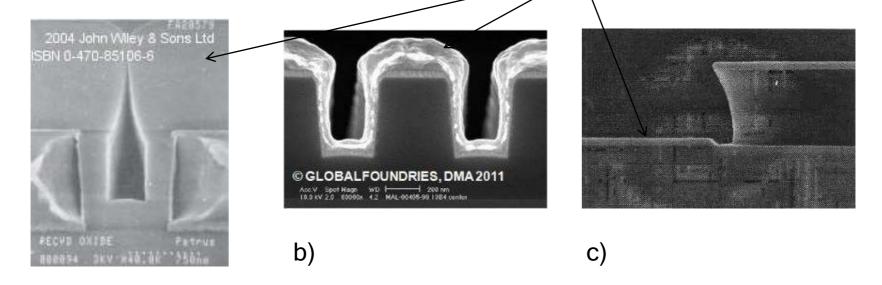

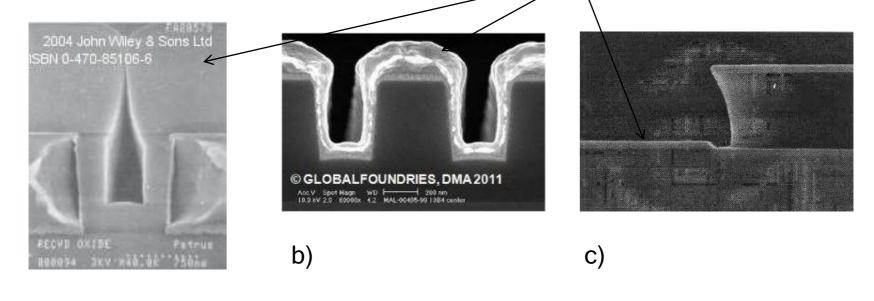

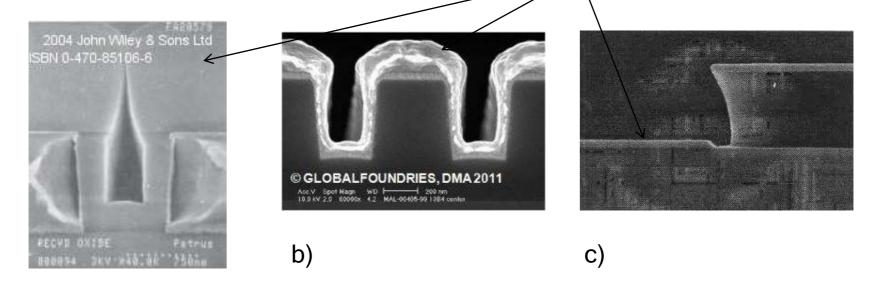

#### Concerns with CVD

Figure 5-15

### + Inherent Uniformity Issues!

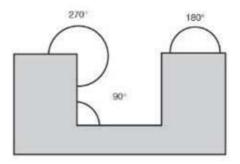

Top, arrival angles of depositing species at different positions; bottom, step coverage, A/H, and bottom coverage, B/H.

Introduction to microfabrication / Sami Franssila ISBN 0-470-85106-6

#### Which deposition technique was used to make the structure below?

#### Which deposition technique was used to make the structure below?

a)

Choices are:

PVD - evaporation, (PE)CVD, PVD - Sputtering

#### Which deposition technique was used to make the structure below?

a)

Choices are:

c) PVD - evaporation,a) (PE)CVD,

b) PVD - Sputtering

### 1 K Memory, IBM 1970

Page: 26 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

### 1 K Memory, IBM 1970

### MPU "Alpha", DEC 1994

## How to avoid parasitic FETs

$$V_{T} = \frac{d_{ox}}{\varepsilon_{ox}} \sqrt{2\varepsilon_{si}eN_{A}(2\Phi_{F} + V_{SB})} + 2\Phi_{F} - \frac{Q_{eff}}{C_{ox}} + \frac{\Delta W_{F}}{e}$$

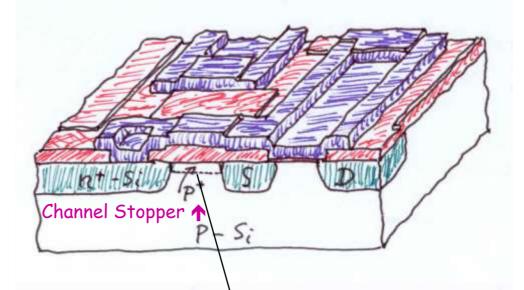

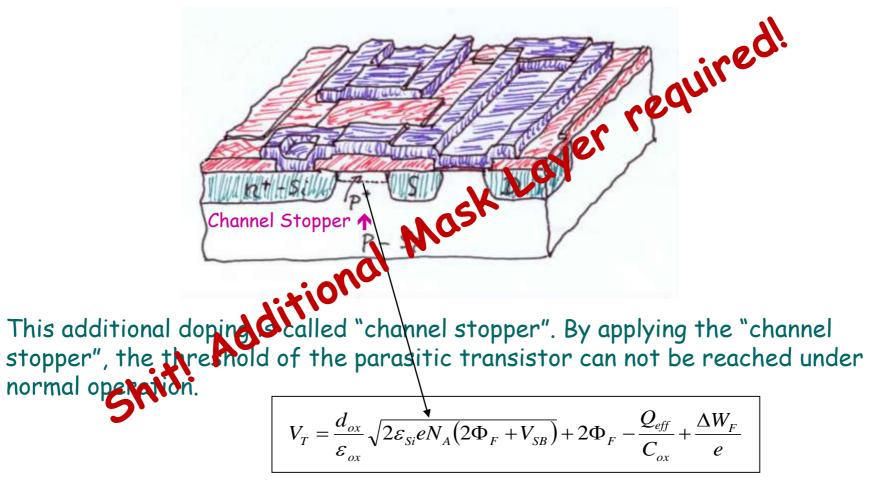

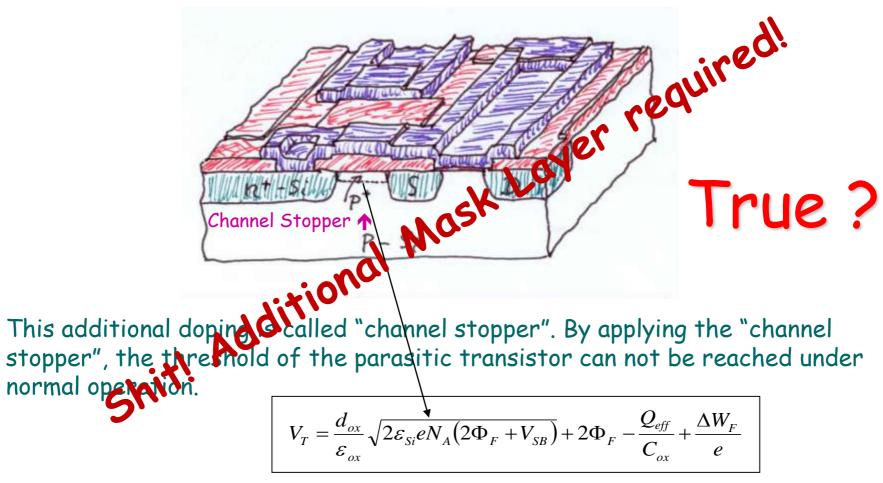

### How to avoid parasitic FETs Innovation: 3.2 a Channel Stop

To further relax this problem, the p-substrate underneath the fieldox can be doped to  $p^+$ . This shifts  $V_T$  of the parasitic transistor to higher  $V_G$  and insures a safer operation.

This additional doping is called "channel stopper". By applying the "channel stopper", the threshold of the parasitic transistor can not be reached under normal operation.

$$V_T = \frac{d_{ox}}{\varepsilon_{ox}} \sqrt{2\varepsilon_{Si}eN_A(2\Phi_F + V_{SB})} + 2\Phi_F - \frac{Q_{eff}}{C_{ox}} + \frac{\Delta W_F}{e}$$

### How to avoid parasitic FETs Innovation: 3.2 a Channel Stop

To further relax this problem, the p-substrate underneath the fieldox can be doped to  $p^+$ . This shifts  $V_T$  of the parasitic transistor to higher  $V_G$  and insures a safer operation.

### How to avoid parasitic FETs Innovation: 3.2 a Channel Stop

To further relax this problem, the p-substrate underneath the fieldox can be doped to p<sup>+</sup>. This shifts  $V_T$  of the parasitic transistor to higher  $V_G$  and insures a safer operation.

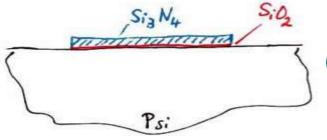

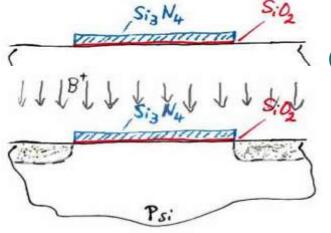

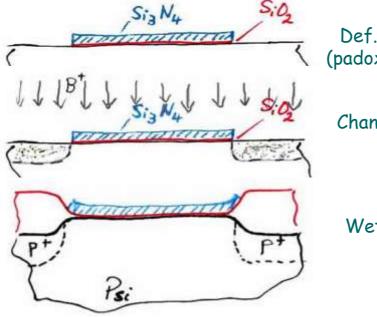

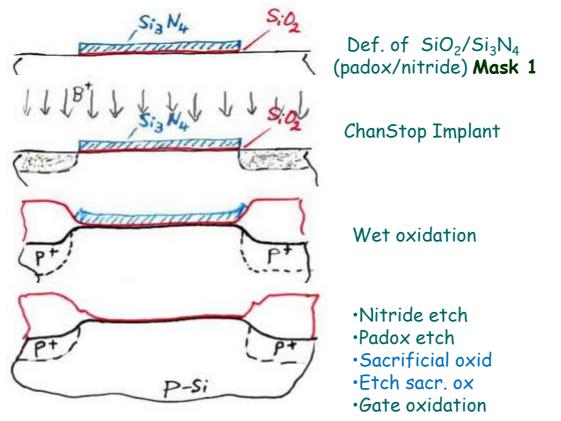

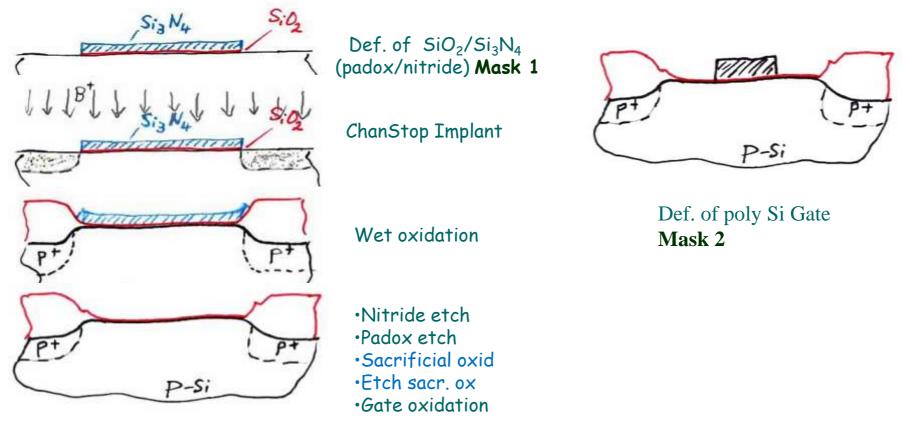

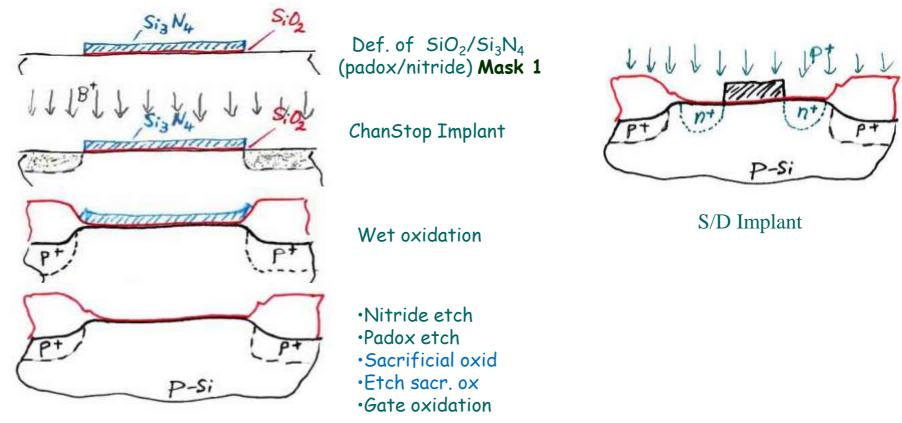

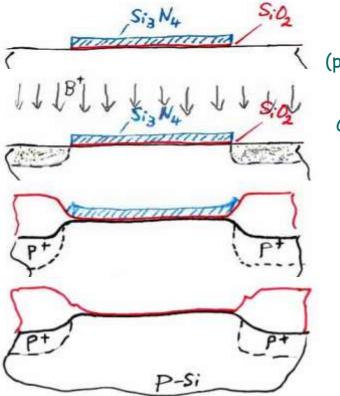

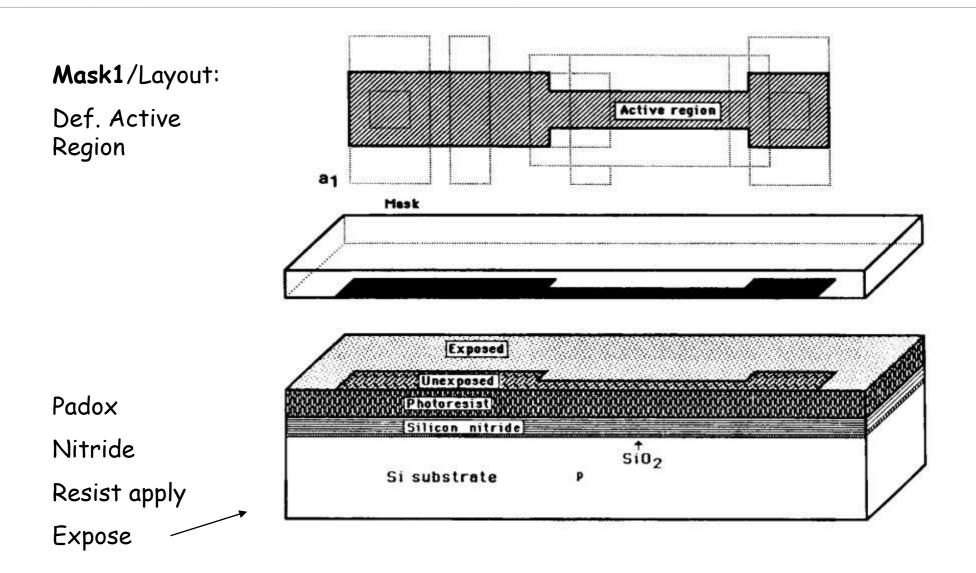

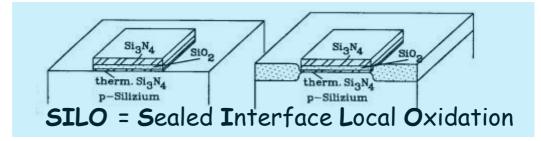

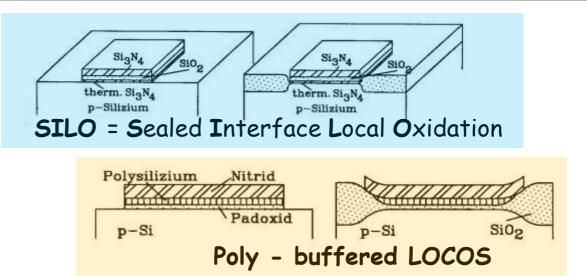

A "self adjusting" way to combine the growth of the fieldox with the masking of the "Channel Stopper" is the so called LOCOS process which stands for Local Oxidation of Silicon. With the following process flow:

A "self adjusting" way to combine the growth of the fieldox with the masking of the "Channel Stopper" is the so called LOCOS process which stands for Local Oxidation of Silicon. With the following process flow:

Def. of SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> (padox/nitride) Mask 1

A "self adjusting" way to combine the growth of the fieldox with the masking of the "Channel Stopper" is the so called LOCOS process which stands for Local Oxidation of Silicon. With the following process flow:

Def. of SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> (padox/nitride) Mask 1

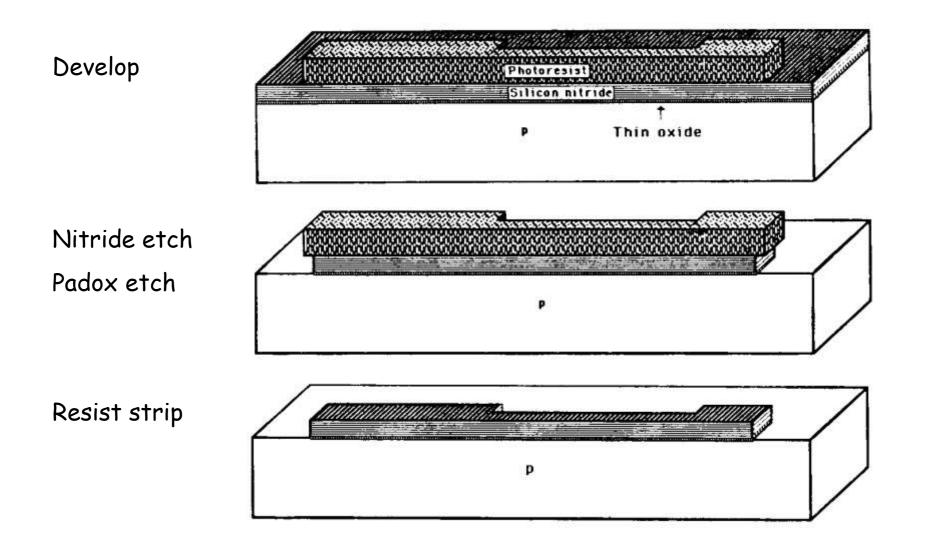

ChanStop Implant

A "self adjusting" way to combine the growth of the fieldox with the masking of the "Channel Stopper" is the so called LOCOS process which stands for Local Oxidation of Silicon. With the following process flow:

Def. of SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> (padox/nitride) Mask 1

ChanStop Implant

Wet oxidation

Page: 35 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

A "self adjusting" way to combine the growth of the fieldox with the masking of the "Channel Stopper" is the so called LOCOS process which stands for Local Oxidation of Silicon. With the following process flow:

A "self adjusting" way to combine the growth of the fieldox with the masking of the "Channel Stopper" is the so called LOCOS process which stands for Local Oxidation of Silicon. With the following process flow:

A "self adjusting" way to combine the growth of the fieldox with the masking of the "Channel Stopper" is the so called LOCOS process which stands for Local Oxidation of Silicon. With the following process flow:

A "self adjusting" way to combine the growth of the fieldox with the masking of the "Channel Stopper" is the so called LOCOS process which stands for Local Oxidation of Silicon. With the following process flow:

Def. of SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> (padox/nitride) Mask 1

ChanStop Implant

Wet oxidation

Nitride etch

Padox etch

Sacrificial oxid

Etch sacr. ox

Gate oxidation

and so on ...

A "self adjusting" way to combine the growth of the fieldox with the masking of the "Channel Stopper" is the so called LOCOS process which stands for Local Oxidation of Silicon. With the following process flow:

Def. of SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> (padox/nitride) Mask 1

ChanStop Implant

#### Wet oxidation

Nitride etch

Padox etch

Sacrificial oxid

Etch sacr. ox

Gate oxidation

- © Self adjusted chanstop

- © Fieldox can be thinner

- Only half of Fieldox thickness contributes to surface topography

- => reduced DOF! or

- => smaller CD!

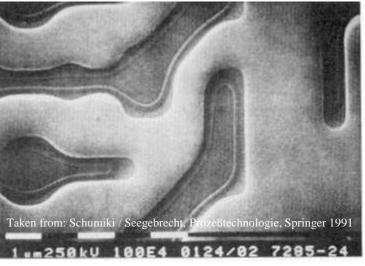

### LOCOS (LOCal Oxidation Process)

Reason for sacrificial oxidation: Si<sub>3</sub>N<sub>4</sub> residue must be removed before gate oxidation!

Page: 41 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

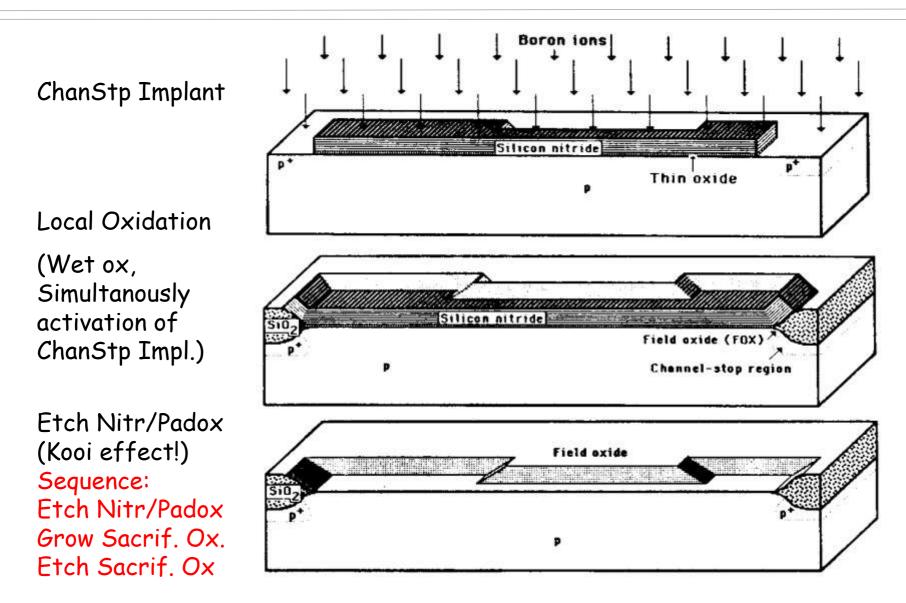

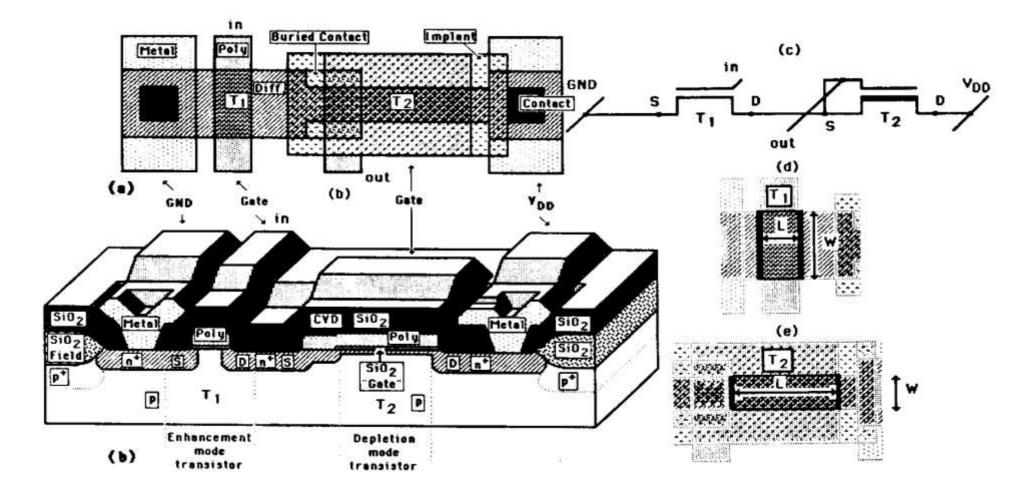

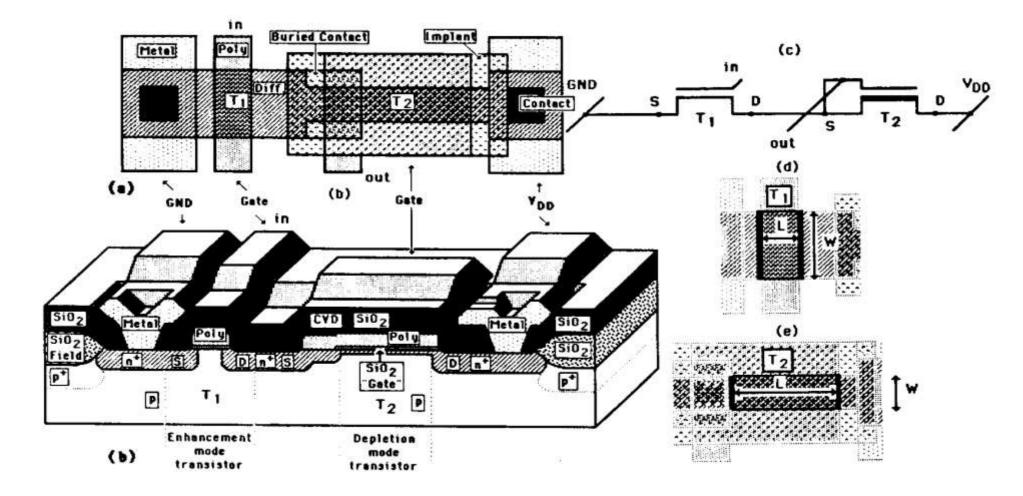

Example: Integration Scheme of an ED Inverter in Si-Gate / LOCOS technique

Page: 42 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

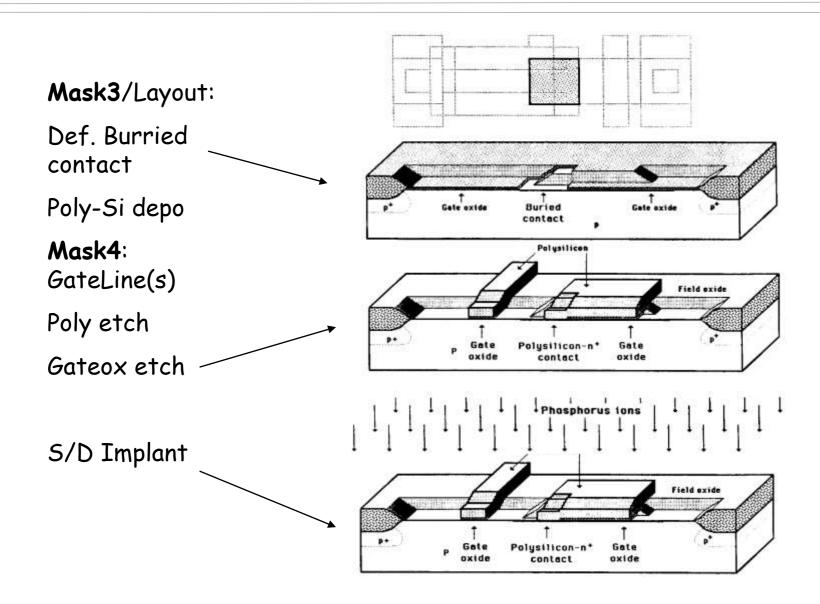

### 3.2.1. E/D Si-Gate LOCOS Inverter Process

### E/D N-MOS Prozess (2)

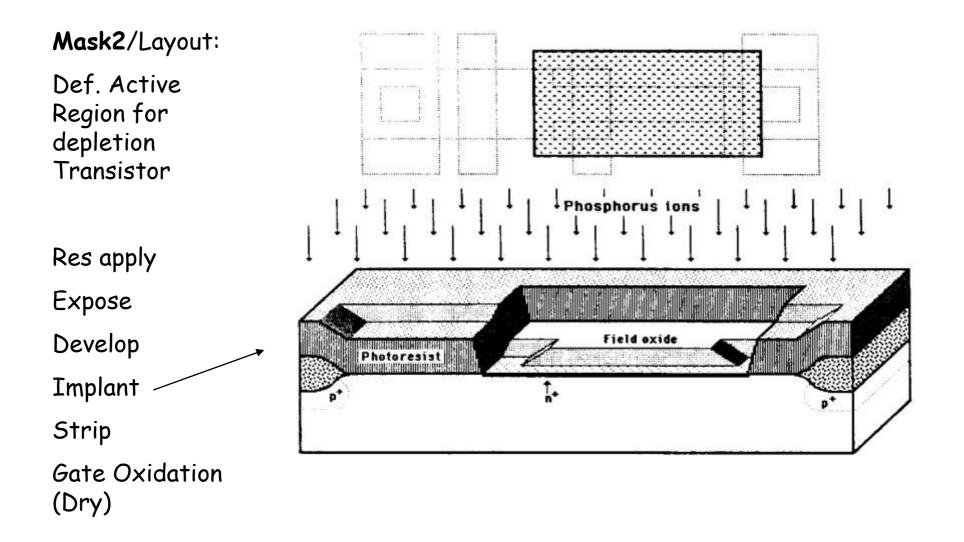

## E/D N-MOS Prozess (3)

## E/D N-MOS Prozess (4)

## E/D N-MOS Prozess (5)

## E/D N-MOS Prozess (6)

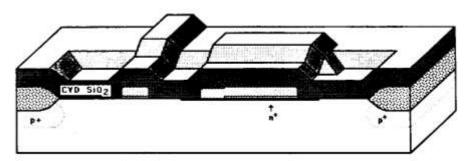

Depo of Insulation oxide (CVD Oxide)

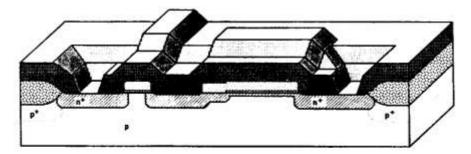

Mask5: MetalContact

Contact etch

Reflow (Activation & diffusion of Implants)

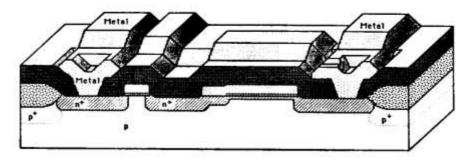

Al Deposition

Mask6: Metal

Metal Etch

Ox - Reflow

### E/D N-MOS Prozess (7)

### E/D N-MOS Prozess (7)

S.Wolf: Si Proc. VLSI ERA

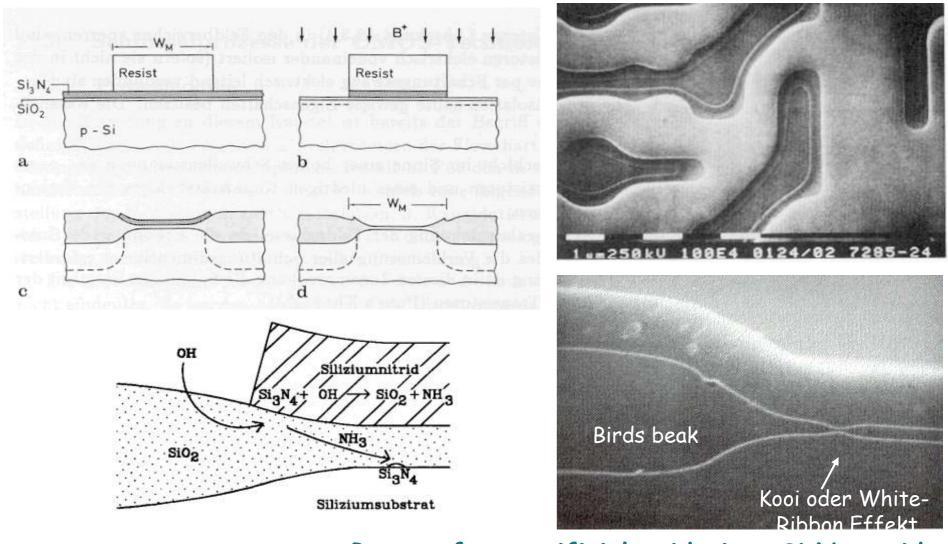

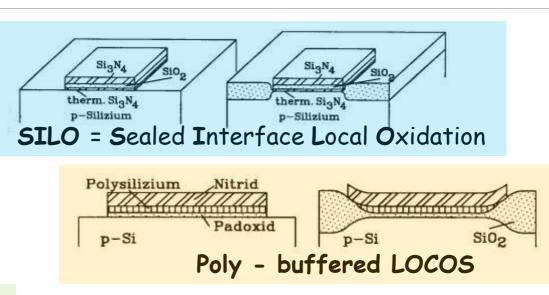

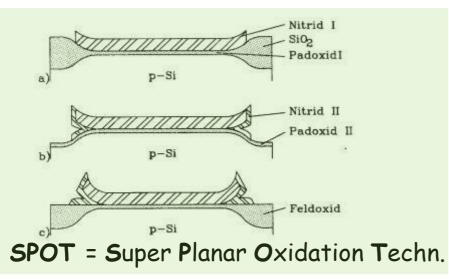

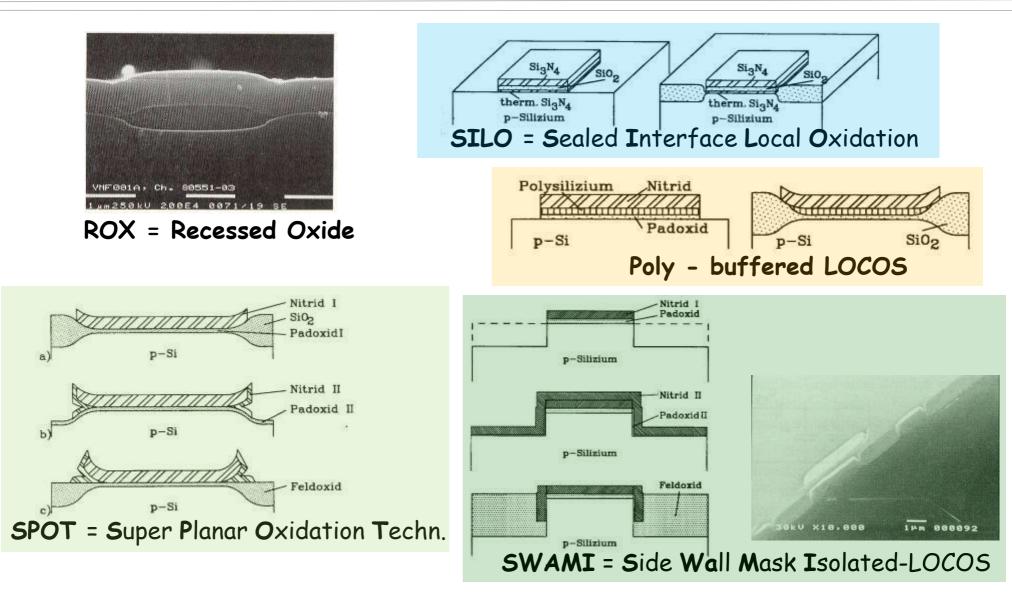

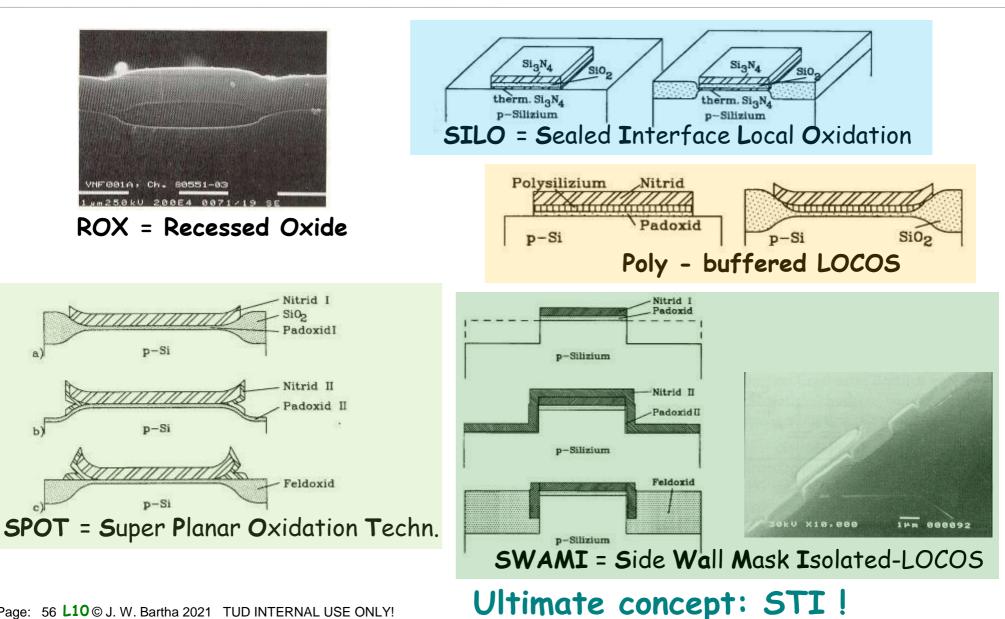

#### targeting DOF & scaling

#### ROX = Recessed Oxide

Page: 51 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

targeting DOF & scaling

ROX = Recessed Oxide

#### targeting DOF & scaling

#### ROX = Recessed Oxide

#### targeting DOF & scaling

ROX = Recessed Oxide

targeting DOF & scaling

targeting DOF & scaling

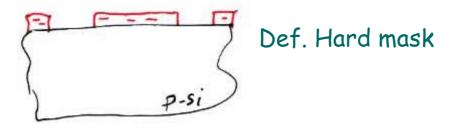

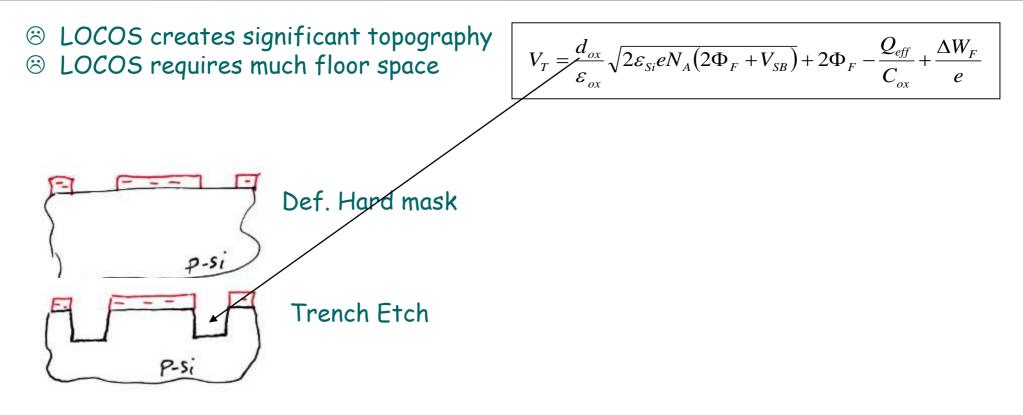

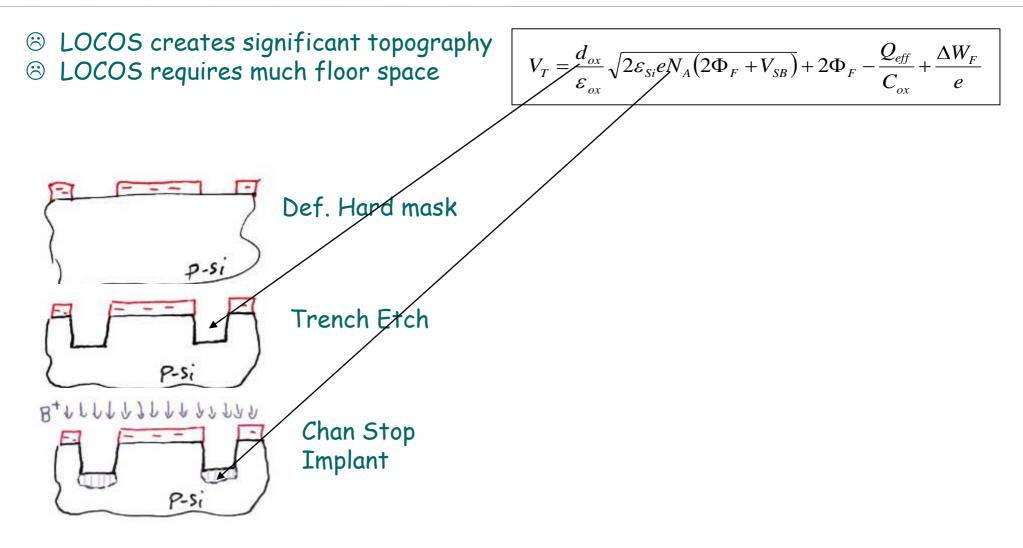

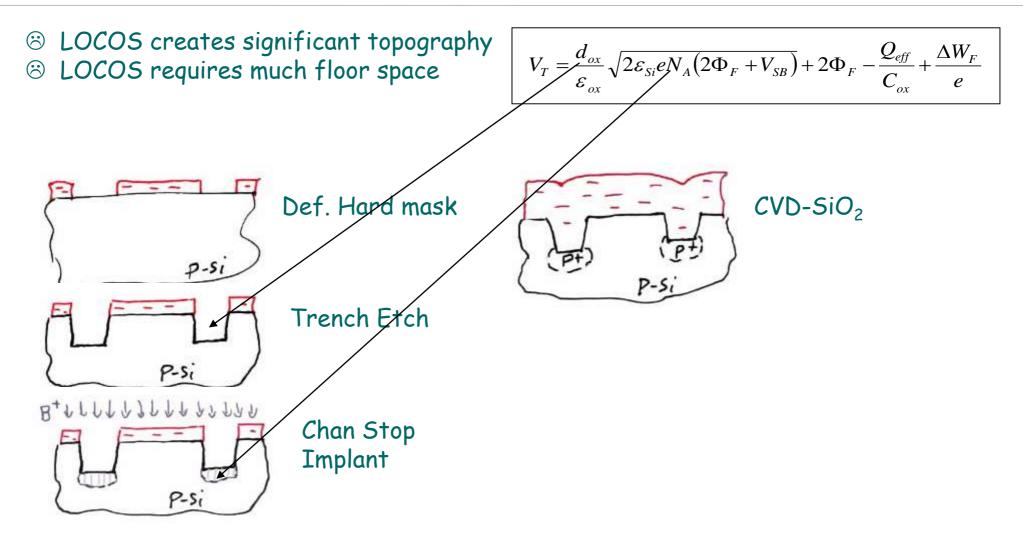

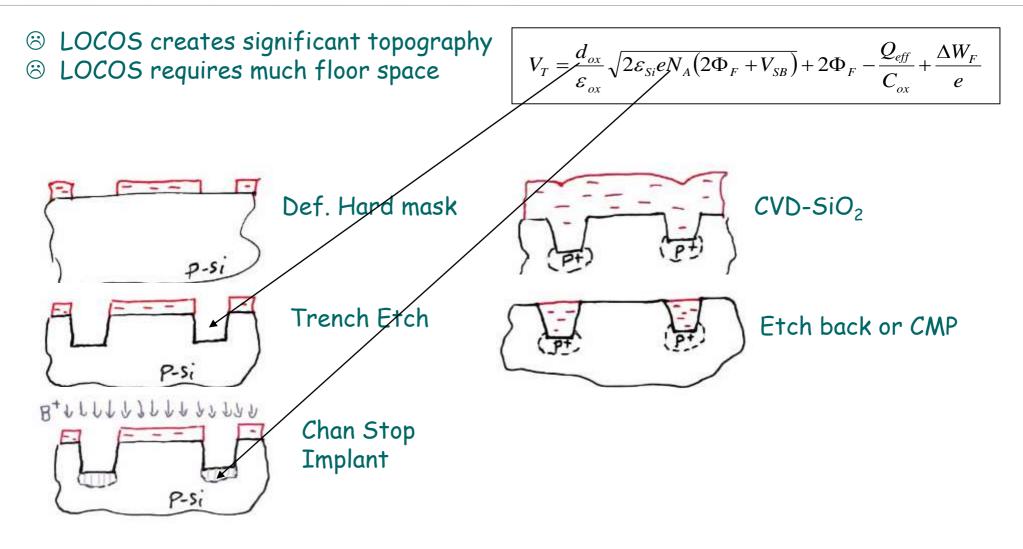

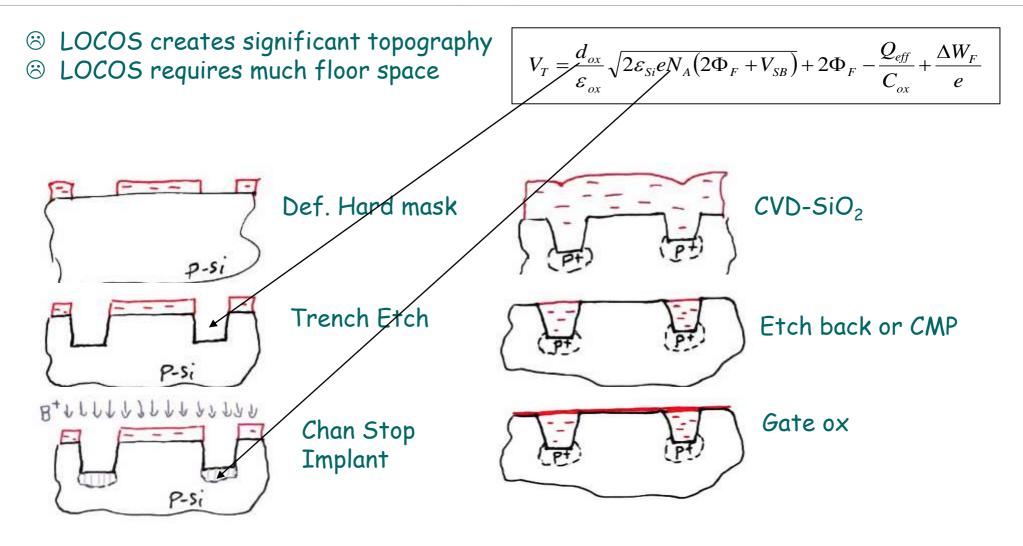

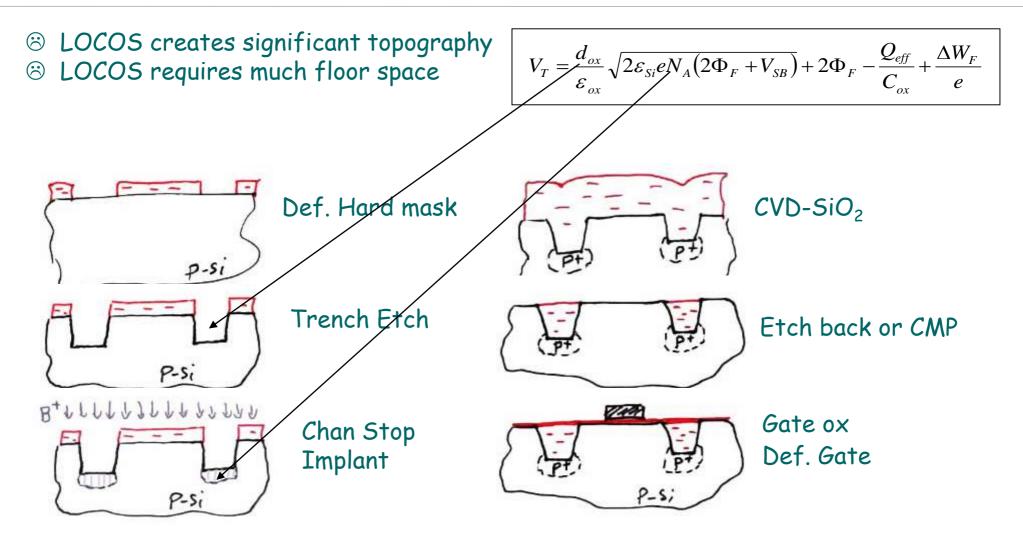

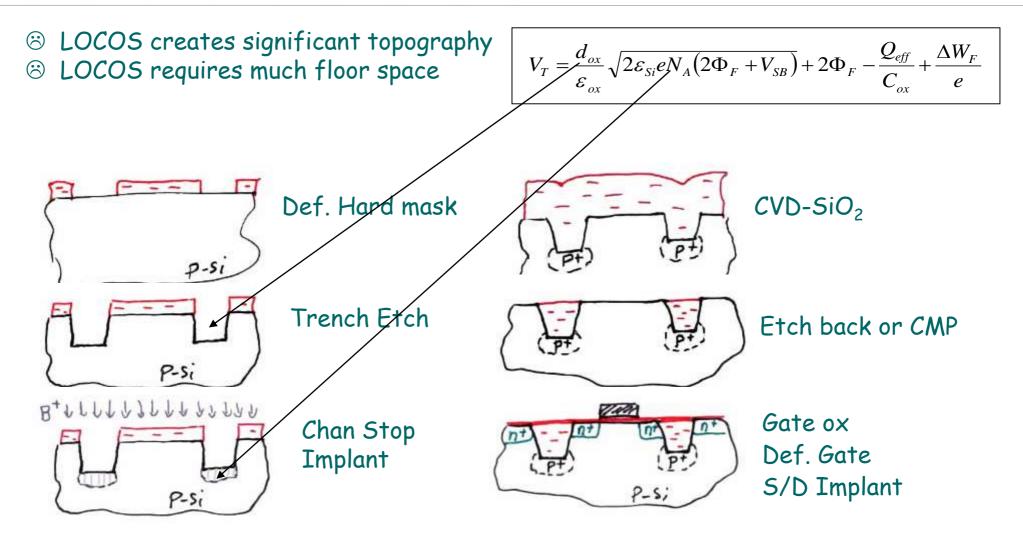

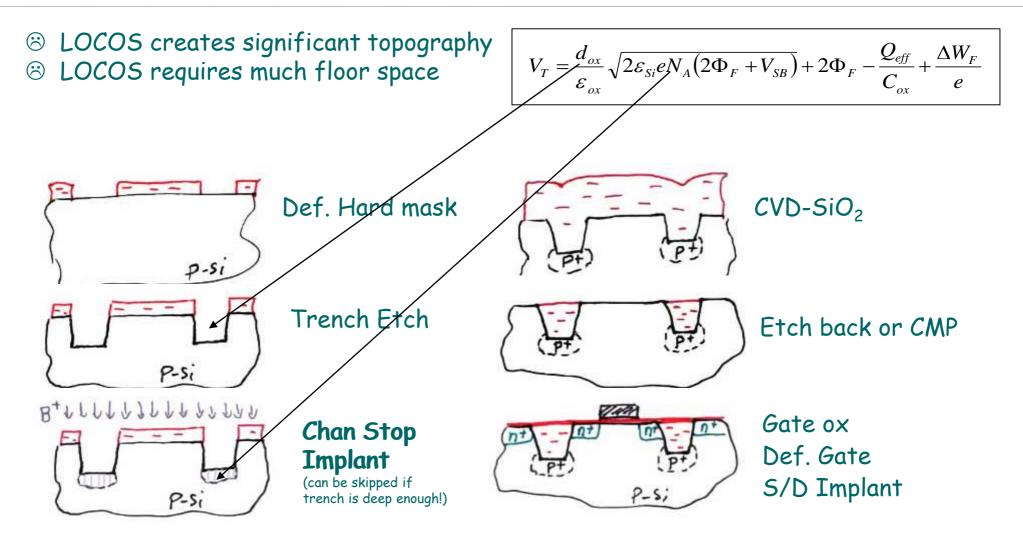

Bodd LOCOS creates significant topography

LOCOS requires much floor space

$$V_T = \frac{d_{ox}}{\varepsilon_{ox}} \sqrt{2\varepsilon_{Si}eN_A(2\Phi_F + V_{SB})} + 2\Phi_F - \frac{Q_{eff}}{C_{ox}} + \frac{\Delta W_F}{e}$$

Bodd LOCOS creates significant topography

LOCOS requires much floor space

$$V_T = \frac{d_{ox}}{\varepsilon_{ox}} \sqrt{2\varepsilon_{Si}eN_A(2\Phi_F + V_{SB})} + 2\Phi_F - \frac{Q_{eff}}{C_{ox}} + \frac{\Delta W_F}{e}$$

thick deposition net -etch CIUP Pol:sh:ng

Page: 67 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!

# »Wissen schafft Brücken.«

Page: 68 L10 © J. W. Bartha 2021 TUD INTERNAL USE ONLY!