Markus Krause - Informationssystemtechnik - Fakultät Informatik

## Energiesparmaßnahmen in Sub-100nm ICs

VLSI-EDA-Lehrstuhl Seminarvortrag von Markus Krause am 06.06.2012

- 1. Gründe für das Senken der Leistungsaufnahme

- 2. Ursachen von Verlustleistung

- 3. Strukturverkleinerung/Absenken von Udd

- 4. Clock-Gating/Scaling

- 5. Power-Gating

- 6. Praktisches Beispiel / Ausblick

- 7. Quellen

- > Allgemein:

- Kühlungsprobleme (Prozessor-Dies haben heute Verlustleistungsdichte in Größenordnung eines Atomreaktors)

- Umweltaspekte

- > HPC: Betriebskosten

- Mobilgeräte: Akkulaufzeit

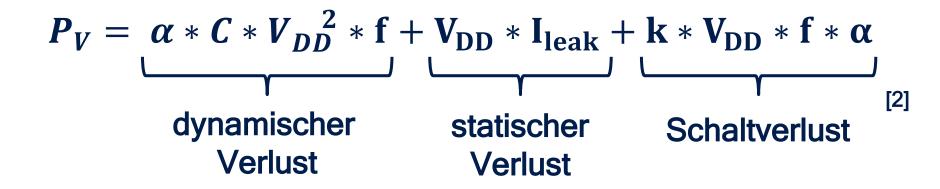

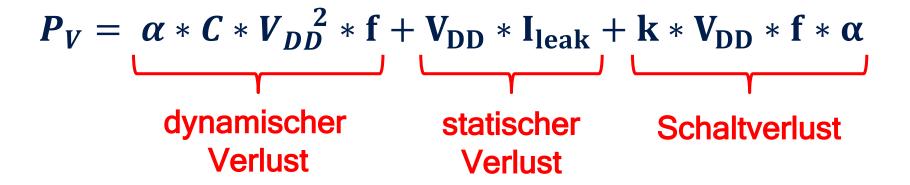

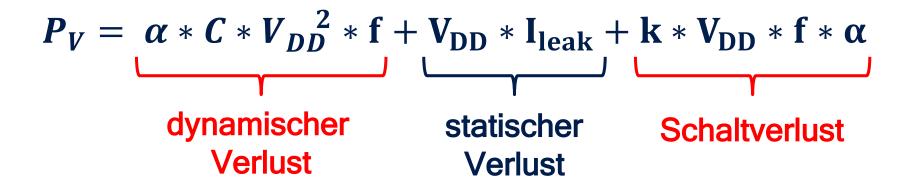

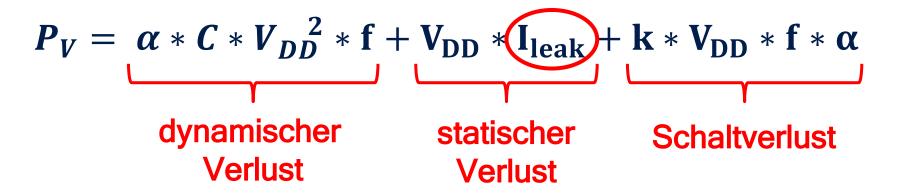

- Es ergeben sich drei "Stellschrauben":

- Betriebsspannung

- > Taktfrequenz

- > Technologie/Strukturbreite

- beeinflusst alle Komponenten, sehr effektiv

- durch Schwellspannung der Transistoren nicht beliebig skalierbar

- muss in der Regel durch kleinere/teurere

Technologie erkauft werden

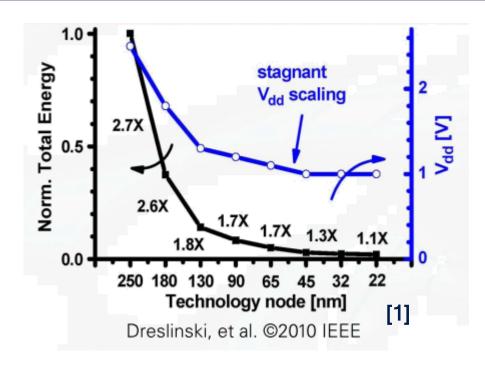

Betriebsspannungsabsenkung in den klassischen

SI-Technologien ist ausgereizt

- Änderung/Abschaltung der Taktfrequenz verspricht lineare Einsparung

- > 3 gängige Varianten

- > 1. Variante: Abtrennung vom Taktbaum

- nicht benötigte Schaltungsteile werden zur Laufzeit durch Transfergates getrennt

- > Anspruch: Transparenz für den Anwender

- dosiert verwenden, sonst zu großer Clock-Skew durch die eingefügten Gates

- exzessive Anwendung vor allem in Mobilgeräten

(Mobilfunkmodems, WLAN, Bluetooth, etc.)

- > 2. Variante: Clock-Domains

- Schaltungsteile, welche nicht zeitkritisch sind, werden langsamer getaktet

- ➤ Übergang z.B. mit FIFO-Puffern

- interessant in heterogenen Systemen

- > 3. Variante: Over-/Underclocking

- Anpassung der Taktfrequenz an die aktuelle Auslastung

- im Durchschnitt erreichen einer TDP-Grenze welche unter der maximalen theoretischen Leistungsaufnahme liegt

- mittlerweile weit verbreitet (z.B. Intel Turboboost, AMD Turbo-Core, Mobil-SoCs)

- Abschaltung der Betriebsspannung einzige

Möglichkeit Leckströme zur Laufzeit zu beeinflussen

- $\succ$  essentiell in modernen Technologien, über die Hälfte von  $P_V$  durch  $I_{leak}$

- Power-Gating ist kompliziert, zahlreiche physikalische Effekte müssen beachtet werden

- Störung von Nachbarblöcken

- extreme Belastung für das Power-Mesh

- komplizierte Timing-Abschätzung

- im Gegensatz zu Clock-Gating im Allgemeinen schwerer zu maskieren, Umschaltung in einem Takt mit viel Aufwand und Know-How verbunden

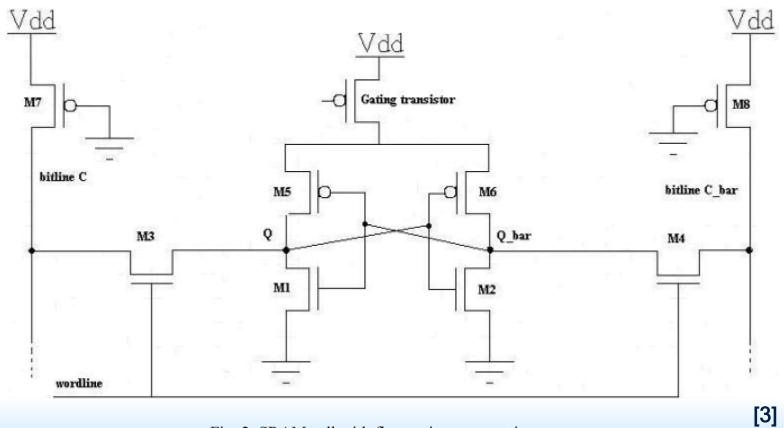

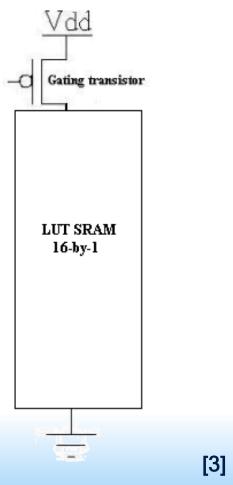

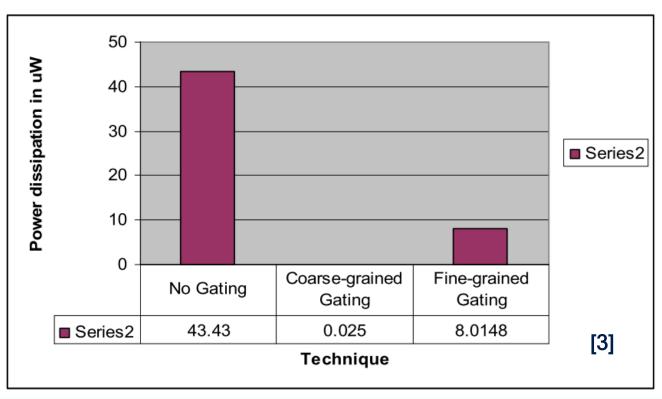

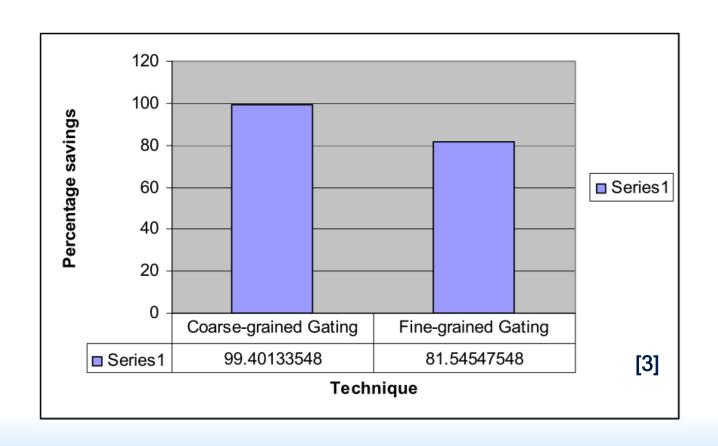

- Vergleich der Effizienz von feingranularem und grobgranularem Abschalten der Betriebsspannung in FPGA-LUTs

- interessant, da viele Energiesparmaßnahmen in FPGAs nicht wie in ASICs implementierbar sind (vom Anwender)

Fig. 2. SRAM cell with fine-grain power gating

- Vorteil: weniger Last beim Ab-/Zuschalten, selektiv

- Nachteil: mehr Power-Gates, mehr Fläche, weniger Einsparung als grobgranulares Gating

Fig. 3. Coarse-gated SRAM array with 16 SRAM cells

- Vorteil: weniger Power-Gates, weniger Fläche, nahezu maximale Einsparung

- Nachteil: mehr Last beim Ab-/Zuschalten, wenig selektiv

Fig. 5. Leakage power dissipation with coarse-grain and fine-grain power gating

Fig. 6 Percentage power savings over no-gating case

- > selektive Abschaltung perspektivisch eine der besten Energiesparmaßnahmen

- ➤ stellt hohe Designanforderungen →

elektrotechnische Kenntnisse aus dem analogen

Bereich gewinnen an Bedeutung

- in programmierbaren Schaltkreisen sind Anbieter gefordert

- Forschung hochaktuell (z.B. Cool Base-Stations im Rahmen von Cool Silicon hier an TU Dresden)

- technologische Maßnahmen gegen Leckströme werden marktbestimmend werden (Silicon-On-Insulator, Tri-Gate-Transistors, alternative Materialien wie Graphen oder Carbon-Nanotubes, Memristorspeicher/-schalter)

- ➤ [1] Near-Threshold Computing: Reclaiming Moore's Law Through Energy Efficient Integrated Circuits, IEEE 2010, Dreslinski

- ➤ [2] VLSI-Prozessorentwurf, TU Dresden, Vorlesung Wintersemester 10/11, Schüffny

- ➤ [3] A comparative analysis of coarse-grain and finegrain power gating for FPGA lookup tables, IEEE 2009, Nair

»Wissen schafft Brücken.«