Vereinbarkeit von partieller Rekonfiguration und Out-of-Context Synthese

Forschungsprojekt

Björn Gottschall Dresden, 18.08.2016

- 1. Motivation

- 2. Begriff der Synthese & Implementierung

- 3. Out-of-Context Synthese

- 4. Partielle Rekonfiguration

- 5. Unterschiede & Fazit

- 6. Praktisches Beispiel

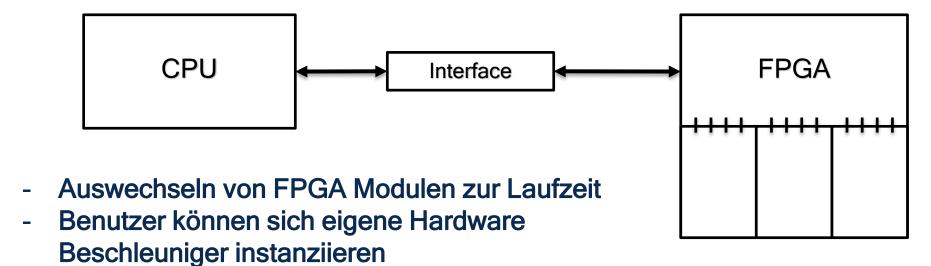

- Unabhängige und isolierte Entwicklung von FPGA Modulen

- Trennung der Ressourcenkonkurrenz auf verschiedenen Ebenen

- Störungen von anderen sollen nicht möglich sein

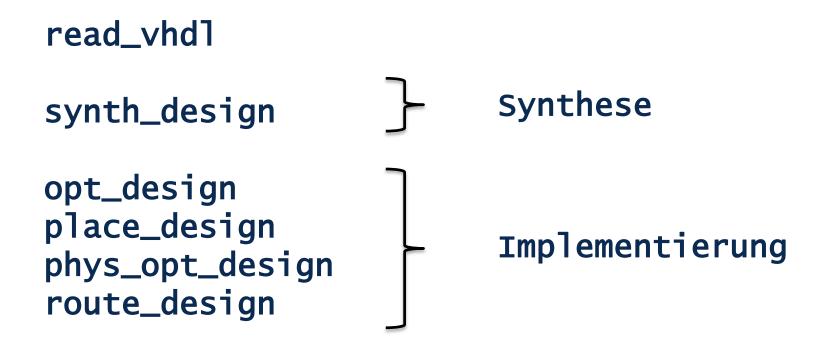

# Begriff der Synthese & Implementierung

Informatik » Institut für Technische Informatik » Professur VLSI-Entwurfssysteme, Diagnostik und Architektur

write\_bitstream

write\_checkpoint

Informatik » Institut für Technische Informatik » Professur VLSI-Entwurfssysteme, Diagnostik und Architektur

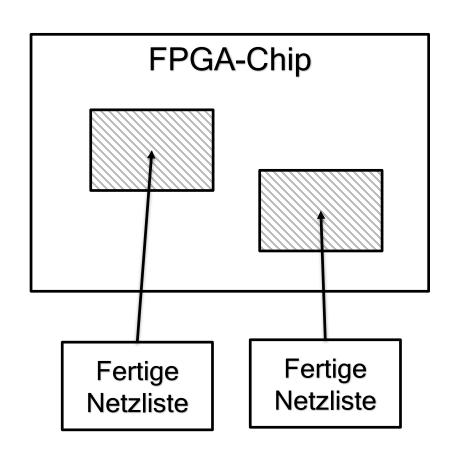

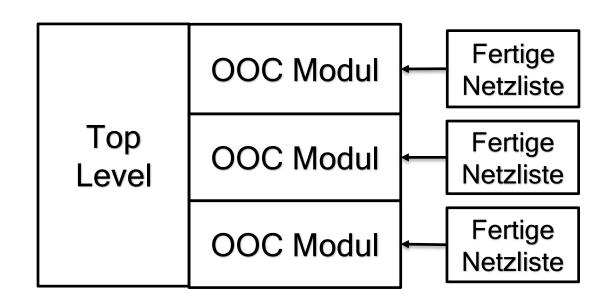

#### Idee der Out-of-Context Synthese

- Unabhängige und isolierte Entwicklung von einzelnen Modulen in festgelegten Bereichen des FPGA Chips

- Jedes Modul erzeugt fertige Netzlisten inklusive des Routings

- Implementierung des Top-Level Designs um die fertigen Module herum

Informatik » Institut für Technische Informatik » Professur VLSI-Entwurfssysteme, Diagnostik und Architektur

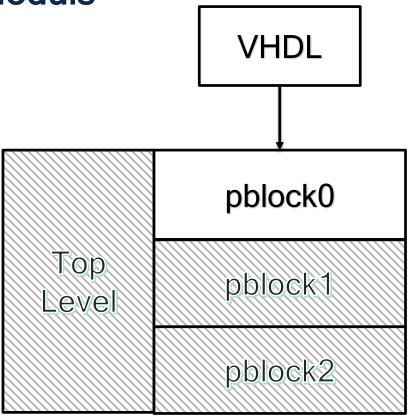

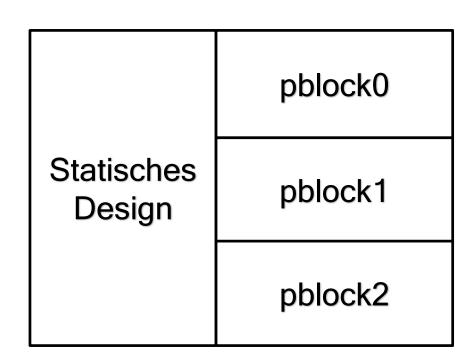

### 1. Aufteilung des FPGAs in geometrische Bereiche

- Top Level Design muss vorhanden sein

- Jedes OOC Modul braucht einen pblock

- Legt Ressourcenverteilung fest

- Definition von interconnects zwischen Top Level und jedem pblock

- Definition des Taktports zu jedem pblock inklusive Frequenz

| Top Level | pblock0 |

|-----------|---------|

|           | pblock1 |

|           | pblock2 |

Informatik » Institut für Technische Informatik » Professur VLSI-Entwurfssysteme, Diagnostik und Architektur

## 2. Entwicklung des OOC Moduls

- Entwickler stehen nur die Ressourcen innerhalb seines pblocks zur Verfügung

- Restliche Entwicklung geschieht wie bei einem gewöhnlichen Top-Level Design

Informatik » Institut für Technische Informatik » Professur VLSI-Entwurfssysteme, Diagnostik und Architektur

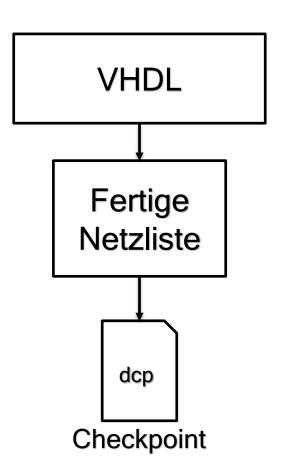

## 3. Synthese und Implementierung

- Synthese mit einem spezielle OOC Flag

- Implementierung mit allen Constraints: pblock, clock, interconnects, routing und placement

- Speichern der erzeugten Netzliste in einem Checkpoint

- Wiederholung für jedes OOC Modul des Gesamtdesigns

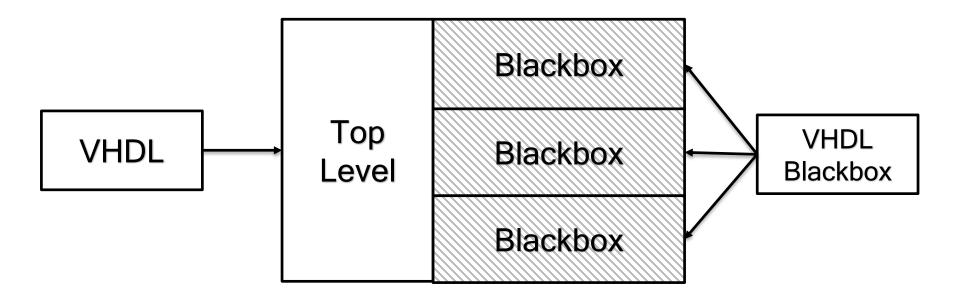

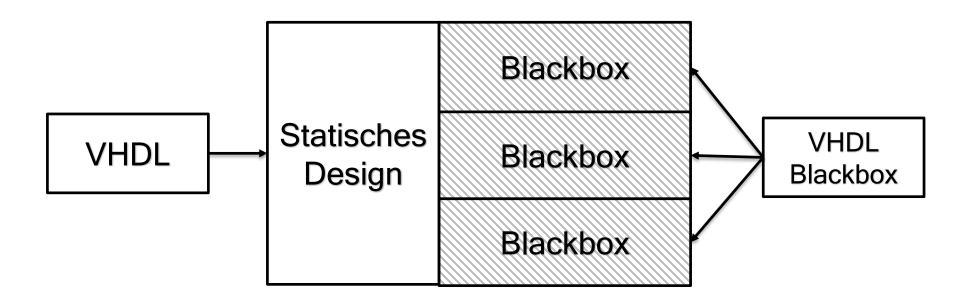

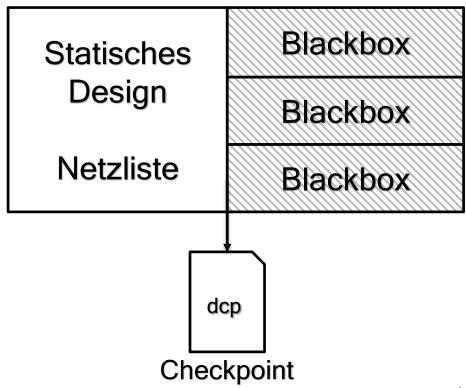

## 4. Synthese des Top-Level Designs

Jedes OOC Modul muss als Blackbox Definition für die Synthese bereit stehen

### 5. Implementierung des Top-Level Designs

- Die Blackboxen werden mit den jeweils fertigen Netzlisten der OOC Module ausgefüllt

- Das Sperren der OOC Module verhindert das die Implementierung diese verändern darf

- Die Implementierung erzeugt nun das fertige Bitfile für den FPGA

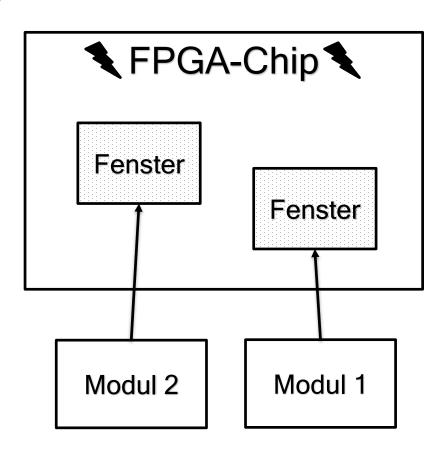

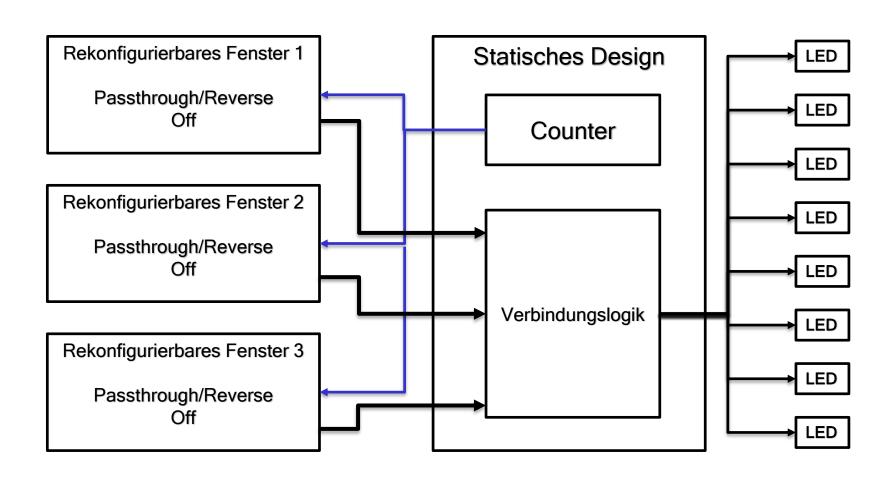

#### Idee der partiellen Rekonfiguration

- Austausch von Modulen innerhalb eines FPGAs zur Laufzeit

- Keine Unterbrechung des FPGAs oder anderer Module

- Aufteilung des FPGAs in statisches Design und rekonfigurierbaren Fenster

- Fixierung des statischen Designs für den Bottom-Up-Entwurf der partiellen Rekonfigurationen

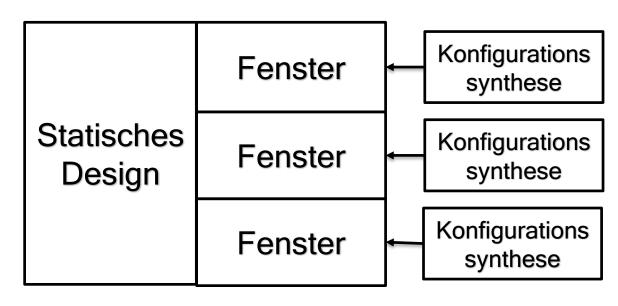

### 1. Aufteilung des FPGAs in geometrische Bereiche

- Aufteilung des FPGA Chips in statisches Design und rekonfigurierbare Fenster

- Jedes rekonfigurierbare Fenster brauch einen pblock

- Jeder pblock darf keine Logik- oder Placement-Ressourcen außerhalb verwenden

- Definition von Interconnects

zwischen Top Level und jedem

pblock sowie des Takts

#### Partielle Rekonfiguration

Informatik » Institut für Technische Informatik » Professur VLSI-Entwurfssysteme, Diagnostik und Architektur

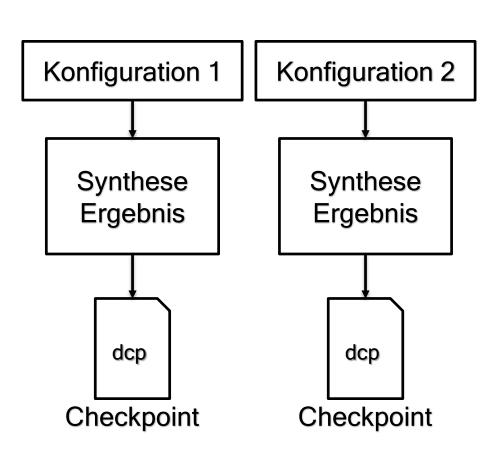

## 2. Synthese der partiellen Konfigurationen

- Synthese von jeder Konfiguration noch unabhängig von seinem Fenster

- Module werden im Out-of-Context Modus synthetisiert

- Speichern des Ergebnis in einem Checkpoint

#### Partielle Rekonfiguration

Informatik » Institut für Technische Informatik » Professur VLSI-Entwurfssysteme, Diagnostik und Architektur

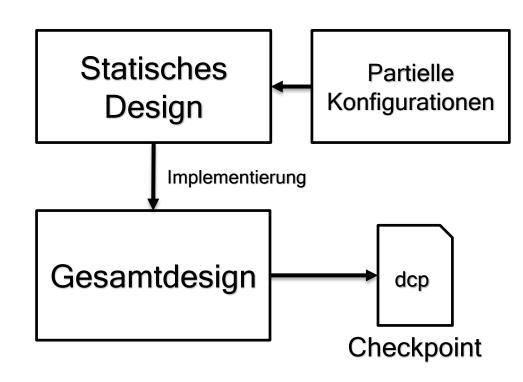

## 3. Synthese des statischen Designs

Jedes rekonfigurierbare Fenster muss als Blackbox Definition bereit stehen

## 4. Implementierung des statischen Designs

- Jedes Fenster besitzt entweder gepufferte Ports oder ist mit einer Implementierung gefüllt

- Es entsteht immer ein fertiges Gesamtdesign

- Markierung von jedem Fenster als rekonfigurierbar

- Laden der Syntheseergebnisse

- Laden aller Constraints

- Implementierung des Gesamtdesigns

#### Partielle Rekonfiguration

Informatik » Institut für Technische Informatik » Professur VLSI-Entwurfssysteme, Diagnostik und Architektur

## 5. Vorbereitung des statischen Designs

Rekonfigurierbaren Fenster werden wieder zu Blackboxen

gewandelt

Sperren des statischen

Designs, damit jede weitere

Implementierung dieses nicht verändern kann

Statisches Design steht nun als Template f

ür jede weitere Implementierung bereit.

## 6. Implementierung der partiellen Rekonfigurationen

festes statisches Design mit Blackboxen laden

- Laden der gewünschten partiellen Konfigurationen

- Implementierung eines Gesamtdesigns

- Speichern als Checkpoint

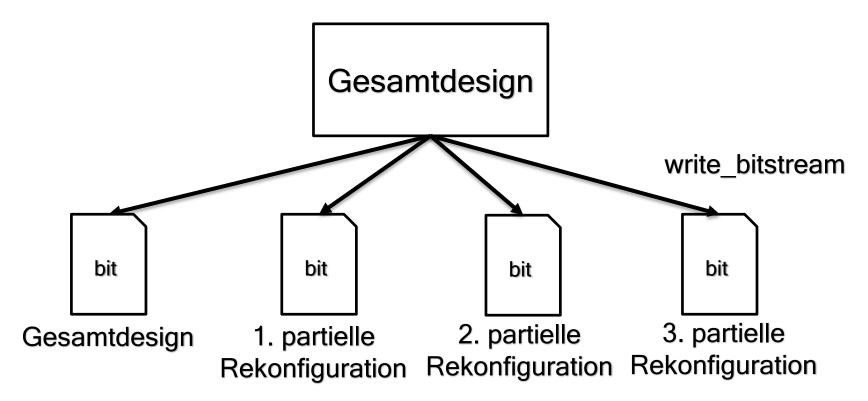

#### 6. Bitstreams der partiellen Rekonfigurationen

Gesamtdesign mit den gewünschten partiellen Konfigurationen laden und Bitstreams schreiben

#### Praktisches Beispiel

Informatik » Institut für Technische Informatik » Professur VLSI-Entwurfssysteme, Diagnostik und Architektur

#### Unterschiede & Fazit

Informatik » Institut für Technische Informatik » Professur VLSI-Entwurfssysteme, Diagnostik und Architektur

### Zusammenfassung

- Die OOC Synthese bietet eine isolierte und unabhängige Entwicklung von einzelnen Modulen

- Nur die partielle Rekonfiguration bietet das Austauschen von einzelnen Modulen in einem statischen Design

- Die Ressourcentrennung ist bei beiden Methoden gleich streng umsetzbar und die Synthese ist sogar identisch

- OOC bietet einen h\u00f6heren Freiheitsgrad bei der Implementierung

- OOC und partielle Rekonfiguration lassen sich noch nicht miteinander kombinieren

- Für das Routing des Top-Level Design konnte nicht garantiert werden, dass diese nicht durch andere Module hindurchgeht.

## Vielen Dank!

- [1] Xilinx UG905: Hierarchical Design, Reuse Design

<a href="http://www.xilinx.com/support/documentation/sw\_manuals/xilinx2012\_3">http://www.xilinx.com/support/documentation/sw\_manuals/xilinx2012\_3</a>

/ug905-vivado-hierarchical-design.pdf

- [2] Xilinx UG702: Partial Reconfiguration (ISE)

<a href="http://www.xilinx.com/support/documentation/sw\_manuals/xilinx14\_1/ug702.pdf">http://www.xilinx.com/support/documentation/sw\_manuals/xilinx14\_1/ug702.pdf</a>

- [3] Xilinx UG909: Partial Reconfiguration (Vivado)

<a href="http://www.xilinx.com/support/documentation/sw\_manuals/xilinx2014\_2">http://www.xilinx.com/support/documentation/sw\_manuals/xilinx2014\_2</a>

/ug909-vivado-partial-reconfiguration.pdf

- [4] Xilinx UG835: Vivado TCL Command http://www.xilinx.com/support/documentation/sw\_manuals/xilinx2014\_4 /ug835-vivado-tcl-commands.pdf