Fakultät Informatik, Institut für Technische Informatik, Professur für VLSI-Entwurfssysteme, Diagnostik und Architektur

#### **Vortrag zum Hauptseminar**

# **Die AHB-Bus-Architektur**

Thomas Dönicke thomas.doenicke@mail.inf.tu-dresden.de

Dresden, 27.05.2009

# Gliederung

- Einführung und Motivation

- Überblick AMBA und Einordnung AHB

- AHB-Funktionsweise

- Zusammenfassung und Ausblick

# Einführung und Motivation

#### Warum SoC und spezielle Busspezifikationen?

- Vorteile SoC:

- sehr kompakt

- niedriger Energieverbrauch

- modularer Aufbau, heutige SoCs bestehen aus vielen einzelnen Systemkomponenten, dadurch:

- fördert Wiederverwendbarkeit

- Kostenersparnis

- Entwicklungszeitersparnis

- spezielle Anforderungen an Bussysteme

- einheitliche Standards wichtig

#### Die verschiedenen Busse (1)

- APB (Advanced Peripheral Bus)

- low-cost interface

- minimal power consumption

- reduced interface complexity

- no pipelining

- Iow-bandwidth

- ASB (Advanced System Bus)

- high performance

- pipelined operation

- burst transfers

- multiple bus masters

#### Die verschiedenen Busse (2)

- AHB (Advanced High-performance Bus)

- Erweiterung bzw. Nachfolger von ASB mit folgenden zusätzlichen Features:

- split transactions

- single-cycle bus master handover

- single-clock edge operation

- non-tristate implementation

- high clock frequency systems

- wider data bus configurations (up to 1024 bits)

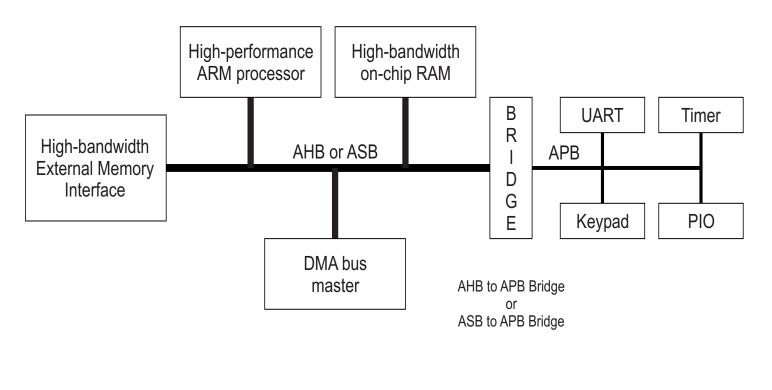

#### ein typisches AMBA-basiertes System

TU Dresden, 27.05.2009

Beispielstruktur

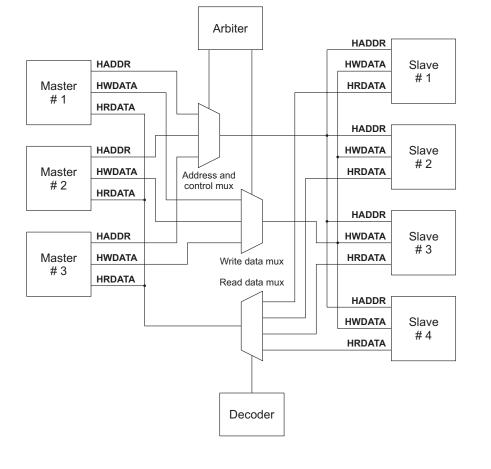

TU Dresden, 27.05.2009

#### Übersicht

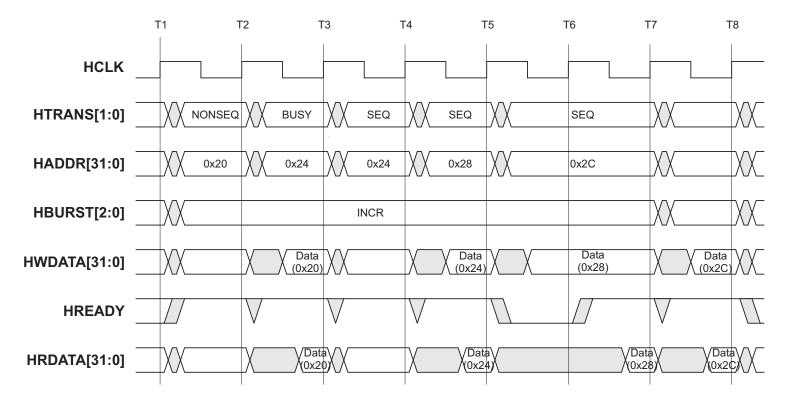

- Basic transfer

- Transfer type

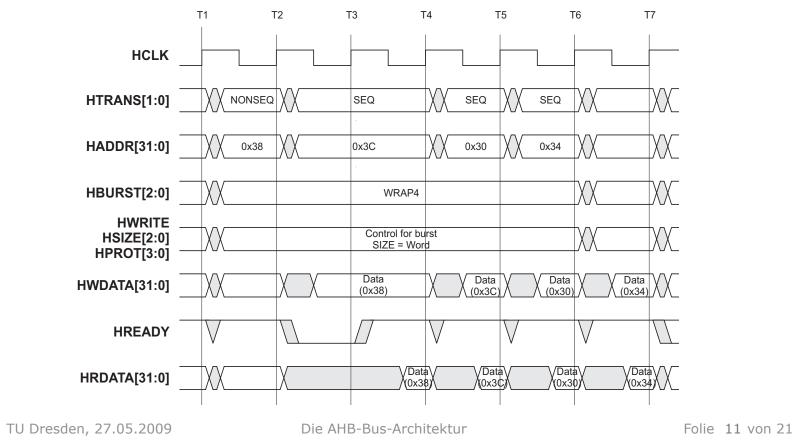

- Burst operation

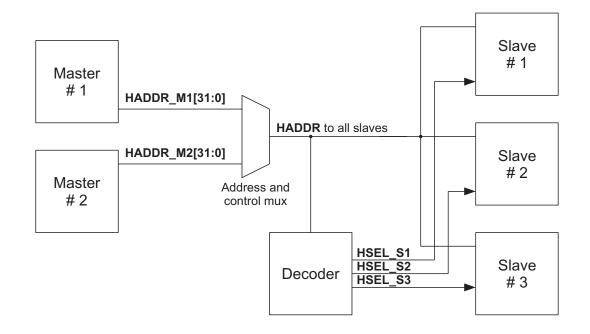

- Address decoding

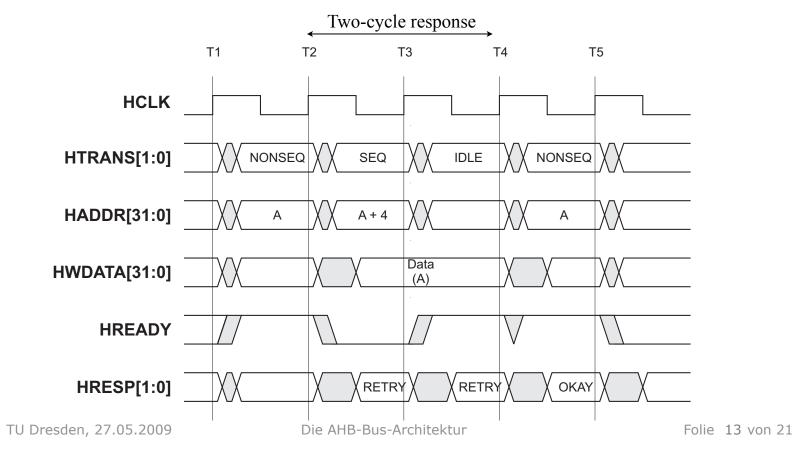

- Slave transfer response

- Arbitration

- Split transfers

- Slave interface diagram

- Master interface diagram

- Arbiter interface diagram

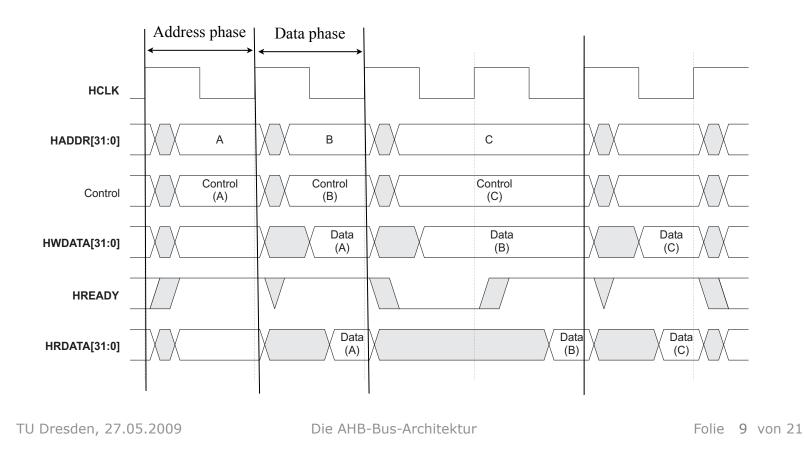

#### Basic transfer

TU Dresden, 27.05.2009

Die AHB-Bus-Architektur

Folie 10 von 21

#### Address decoding

#### Slave transfer response

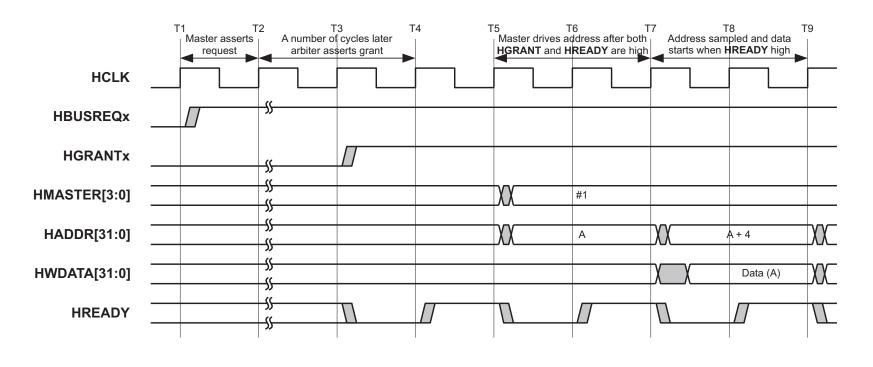

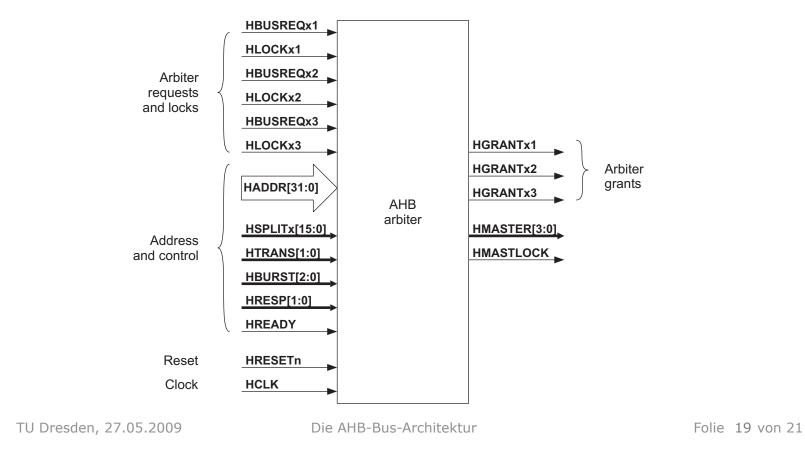

#### Arbitrierung (1)

folgende zusätzliche Signale erforderlich:

- HBUSREQx

- HLOCKx

- HGRANTx

- HMASTER[3:0]

- HMASTLOCK

- HSPLIT[15:0]

### Arbitrierung (2)

TU Dresden, 27.05.2009

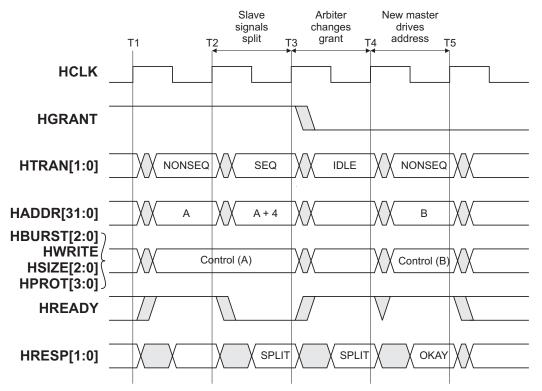

#### Split transfers

TU Dresden, 27.05.2009

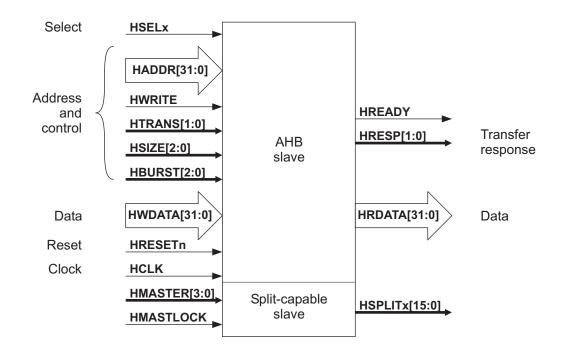

#### Slave interface diagram

TU Dresden, 27.05.2009

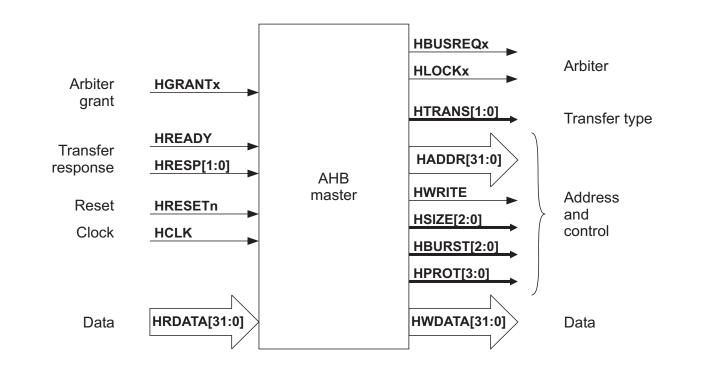

#### Master interface diagram

TU Dresden, 27.05.2009

#### Arbiter interface diagram

# Zusammenfassung und Ausblick

- Einsatz:

- nicht nur von ARM, IP-Cores von vielen anderen Herstellern erhältlich

- ARM bietet selbst viele Cores an: Prime Cell Peripherals

- UARTs

- SDRAM und FLASH memory controller

- DMA engines etc.

- ARM bietet Testbenches und Design Kits sowie vorgefertigte Busmaster an

- AMBA 3.0

- AXI (Advanced eXtensible Interface)

- burst-based transactions with only start address issued

- out-of-order transaction completion

- five unidirectional channels with flexible relative timing

- ATB (Advanced Trace Bus)

# Vielen Dank für Ihre Aufmerksamkeit!

TU Dresden, 27.05.2009 Die AHB-Bus-Architektur

Folie 21 von 21