Fakultät Informatik Institut für Technische Informatik Professur für VLSI-Entwurfssysteme, Diagnostik und Architektur

# Die VIA Nano-Prozessor Architektur

Dresden, 20.05.2009

# Gliederung

- Einführung

- Der Nano

- Modelle

- Architektur Highlights

- Sicherheitsfunktionen

- Energiemanagement

- Cache subsystem

- Struktur

- Intel Atom

- Performance

# 01 Einführung

- Nano ist komplette Neuentwicklung

- von Centaur Technology entwickelt

- Ziel:

- Leistungssteigerung zum C7

- Aber: Strombedarf so gering wie möglich

- Warum?:

- Wachsender Bedarf an Energie-Effizienz

- Mobile computing

- Steigende perfomance Anforderungen (Multimedia)

TU Dresden, 27.05.2009

### 02 Der NANO in Fakten

- 64 Bit Architektur

- Basiert auf VIA Isaiah Architektur

- 65 nm Technologie

- Out-of-order Issue und Execution

- Pin-Kompatible zu C7

- 64 Kbyte L1-Instruction Cache

- 1 MB L2 Cache

- Spezieller Prefetch-Cache

- 95 Millionen Transistoren

- TDP von 5-25 W

### 03 Modelle

| Processor<br>Brand | Model<br>Number | Speed    | VIA V4 FSB | TDP (max) | Process<br>Technology | Idle Power |

|--------------------|-----------------|----------|------------|-----------|-----------------------|------------|

| VIA Nano™          | L2100           | 1.8GHz   | 800MHz     | 25 watts  | 65nm                  | 500mW      |

| VIA Nano™          | L2200           | 1.6GI Iz | 800MHz     | 17 watts  | 65nm                  | 100mW      |

| VIA Nano™          | U2400           | 1.3+GHz  | 800MHz     | 8 watts   | 65nm                  | 100mW      |

| VIA Nano™          | U2350           | 1.3GHz   | 800MHz     | 8 watts   | 65nm                  | 100mW      |

| VIA Nano™          | U2500           | 1.2GHz   | 800MHz     | 6.8 watts | 65nm                  | 100mW      |

| VIA Nano™          | U2300           | 1.0GHz   | 533MHz     | 5 watts   | 65nm                  | 100mW      |

L2100, L2200 (low voltage);

# 04 Architektur Highlights

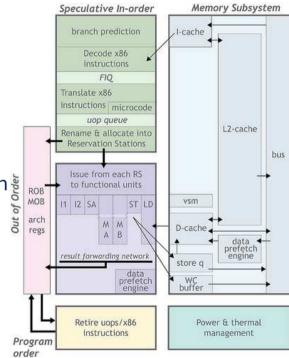

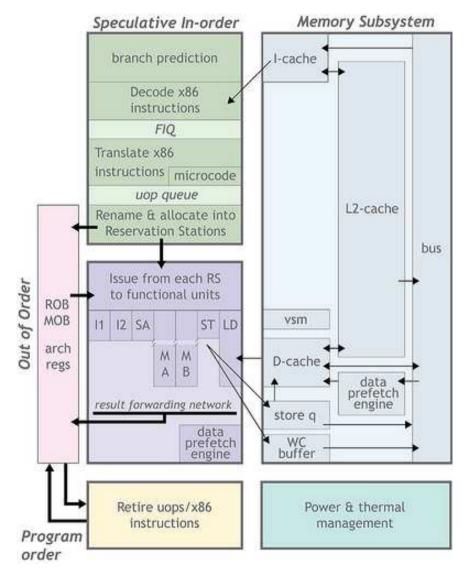

- Superskalar und spekulative in-order fetching

- kann 3 x86 Befehle pro Takt dekodieren

- Out-of-order execution

- Macro- und Micro-fusion

- Performancesteigerung durch Befehlskombination

- Branch-prediction

- 8 verschiedene Vorhersagen in 2 Pipelinestufen

- Sicherheitsfunktionen

- Energiemanagement

- Cache-Subsystem

### 04 Sicherheitsfunktionen

### Überblick

- Verfügt über VSM

- Secure execution mode

|                               | AMD Phenom | Intel Core2 | Intel Atom | VIA C7                                                                                   | VIA Nano                                                                                 |

|-------------------------------|------------|-------------|------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Secure Hash                   | Nein       | Nein        | Nein       | Full SHA-1 &<br>SHA-256<br>5Gb/s Spitze                                                  | Full SHA-1 &<br>SHA-256<br>5Gb/s Spitze                                                  |

| Buffer Overflow               | NX Bit     | NX Bit      | NX Bit     | NX Bit                                                                                   | NX Bit                                                                                   |

| Chipeigene<br>Verschlüsselung | Nein       | Nein        | Nein       | Volle AES Ver-/Entschlüsselung RSA Beschleunigung CBC, CFB-M, AC, CTR Modi 25Gb/s Spitze | Volle AES Ver-/Entschlüsselung RSA Beschleunigung CBC, CFB-M, AC, CTR Modi 25Gb/s Spitze |

| Zufalls-<br>generierung (RNG) | Nein       | Nein        | Nein       | 2 erweiterte<br>Hardware RNG's bis<br>zu 12Mb/s<br>Feeds Output an<br>SHA Engine         | 2 erweiterte<br>Hardware RNG's bis<br>zu 12Mb/s<br>Feeds Output an<br>SHA Engine         |

### 04 Energiemanagement

### **PowerSaver Technology**

- Über P-States beschrieben

- P-States = Kombination aus Betriebsspannung und Takt-Faktor

- Energiemanagement in 3 Phasen abgewickelt

- 1. unverzögertes Umschalten auf andere PLL

- 2. Spannung um kleinstes Delta verändern

- 3. Wiederholung bis Endpunkt erreicht ist

- Bus und Ausführungseinheiten können währenddessen benutzt werden

- Automatisches Ändern der P-States → basiert auf Temperatur

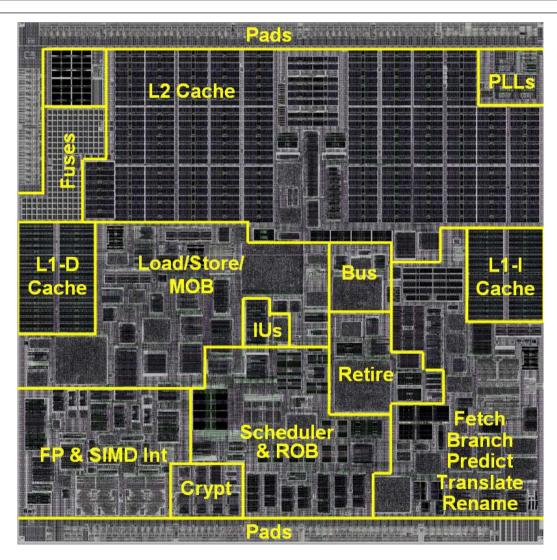

### 04 Cache Subsystem

- Getrennter Daten- und Befehlscache

- 64 kByte

- 16-way set associative

- L2 Cache mit 1 MB

- L1, L2 sind Exclusive Caches

- speziellen prefetch-cache

- Volatile secure memory

- Nur im "secure execution"-Modus erreichbar

- Speicher hat eigenen Adressbereich

TU Dresden, 27.05.2009

Folie 9

# 04 Cache Subsystem exclusive vs inclusive Cache

#### exclusive

- Datum befindet sich in L1 <u>oder</u> L2

- Mehr Daten können gespeichert werden

- Aber Verwaltung komplizierter

- AMD Athlon

### inclusive

- Datum befindet sich in L1 und L2

- Intel Pentium II, III, 4

TU Dresden, 27.05.2009

### 05 Struktur

TU Dresden, 27.05.2009

Folie 11

### 05 Struktur

### 06 Intel Atom

### **Merkmale**

- In-order Verarbeitung, 2 μOps pro Takt

- Hyperthreading

- 45 nm Technologie

- L1-Cache: 32 kB Instruction / 24 kB Data

- L2-Cache: 512 kB, 8-fach assoziativ

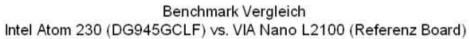

### 07 Performance

### 08 aktuelle Produkte

Jetway JNF77-N1GL-LF P 1,0GHz Mini-ITX NANO-CPU

### 10 Quellen

- C't Magazin (08/2009) Seite 74

- C't Magazin (07/2009) Seite 150

- Isahia Architecture Whitepaper

- http://www.via.com.tw/en/downloads/whitepapers/processors/WP080124Isaiah-architecture-brief.pdf

- VIA Nano Whitepaper

- http://www.via.com.tw/en/downloads/whitepapers/processors/WP080529VIA\_Nano.pdf

- EpiaCenter

- http://www.epiacenter.de/modules.php?name=Content&pa=showpage&pid=256

- Zdnet

- http://www.zdnet.de/bildergalerien\_benchmarks\_via\_nano\_schneller\_als\_intels\_atom\_story-39002383-39194222-1.htm#sid39194225

TU Dresden, 27.05.2009