# Neue Wege im Hochleistungsrechnen: Rekonfigurierbares Computing am Beispiel der RASCTechnologie von SGI

Markus Vogel

s2330460@inf.tu-dresden.de

#### Gliederung

- > Rekonfigurierbares Computing

- Begriffsdefinition

- Bisheriger technischer Stand, Probleme

- Aktuell neue Entwicklungen

- > SGI RASC

- Einblick in die Altix-Linie

- Systemarchitektur eines RASC-Blade

- Vorgesehene Anwendungen

- Programmierumgebung

- > Ausblick auf zukünftige Entwicklungen

- > Fragen/Diskussion

# Rekonfigurierbares Computing Begriffsdefinition

- Computers that modify their hardware circuits as they operate - opening a new era in computer design.

- Zeitschrift Scientific American (Juni 1997)

- > Grundgedanke:

- Neuverdrahtung der Hardware zur Laufzeit

- > Technische Basis:

- FPGAs

# Rekonfigurierbares Computing Verbreitung von FPGAs

- > Eingebettete Systeme, Firmware, DSPs, ...

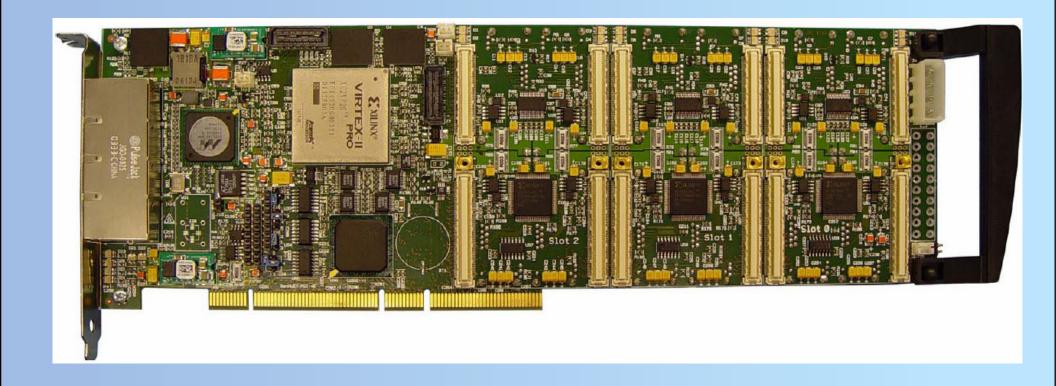

- > Beschleuniger-Boards für Mikrorechner

- Ein oder mehrere FPGAs pro Board

- Idealerweise schnelle Busanbindung (PCI-X)

- Idealerweise onboard-Ram und direkten I/O (Bus ist langsam)

- Mehrere Boards pro PC möglich

- Ansteuerung über Treiber und API

- Viele Systeme, viele Hersteller

- XESS Corporation (www.xess.com SILICON SOFTWARE (www.silicon-software.com)

- CELOXICA (www.celoxica.com)

- ALPHA DATA (www.alpha-data.com)

CESYS (www.cesys.com)

- Associated Professional Systems (www.associatedpro.com)

- TRAQUAIR (www.traquair.com)

- AMONTEC (www.amontec.com/chameleon.shtml)

- NALLATECH (www.nallatech.com)

- COMPAQ (www.research.compaq.com/SRC/pamette)

#### > Nallatech BenNUEY-PCI-4E

# Rekonfigurierbares Computing Konfigurationen

- Netzwerk Rekonfigurierbarer Computer (NORC)

- Job management system, load sharing facility

- Ziel: Auslastung der teuren Geräte erhöhen

- Große Probleme können berechnet werden

- > Rekonfigurierbare Cluster (RCC)

- Pile of PCs (POP), schnelles Netzwerk

- Linux und die Tools der Kartenhersteller

# Rekonfigurierbares Computing Beispiel

- > HPTi (High Performance Technologies Inc.)

- 48 PCs mit 96 FPGAs

- Xilinx Virtex-II

- 34 Tops mit Standardkomponenten

### Rekonfigurierbares Computing Probleme mit FPGAs

- > Aufwendiger Design-Zyklus

- Spezifikation, HDL, Simulation, Synthese, Simulation, Mapping, Placing, Simulation, Programmierung, Test

- > Tools und Software stammt von Herstellern

- Zielgruppe: Hardwareentwickler

- Beschleuniger-Boards:

- Bus-Flaschenhals (datenintensive Probleme)

- Latenzen beim Rückschreiben (Slave)

- Management-Overhead

### Rekonfigurierbares Computing Probleme mit PCs

- > Taktfequenz stagniert

- Leistungsverbrauch steigt, Kühlungsprobleme

- Baugröße wird verringert, Ausbeute sinkt, Kosten steigen

- Kosten limitieren

- > Verdoppelung der Cores

- Fortsetzung von Moores Law

- Leistungsverbrauch steigt

- Probleme mit Busanbindung

- Probleme mit Parallelisierung

- > FPGAs wachsen derzeit schneller als µP-Bereich!

### Rekonfigurierbares Computing Probleme mit HPC

#### > Amdahls Law

- Bei Parallelisierung skaliert nur der parallelisierbare Teil

- Beispiel: bei 90% parallelem Anteil und 9 CPUs: S=5 erhöht man auf 27 CPUs: S=7.5 (Limit: S=10)

- > Leistungsverbrauch, Kühlung, Infrastruktur

- Beispiel: Itanium-II CPU braucht 100W bei 99% parallelem Anteil und 99 CPUs: S=50

Problem: 9,9kW Leistungsaufnahme!

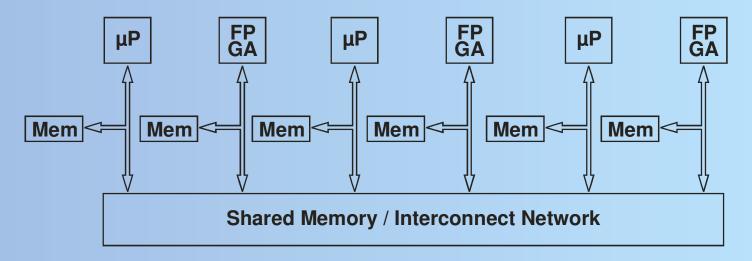

### Rekonfigurierbares Computing **Aktueller Ansatz**

#### Neues Konzept

Mikroprozessoren und FPGAs gleichberechtigt im System

- > Sowohl im PC als auch im HPC-Bereich

- > Beispiele

- NEC Dynamic Reconfigurable Processor Architecture (DRP)

- SRC 6E-Linie, Cray XD1-Linie, SGI Altix-Linie

#### sgi RASC Übersicht

#### > RASC

- Reconfigurable Application Specific Computing

- Verfügbar für Altix-Hochleistungsrechner

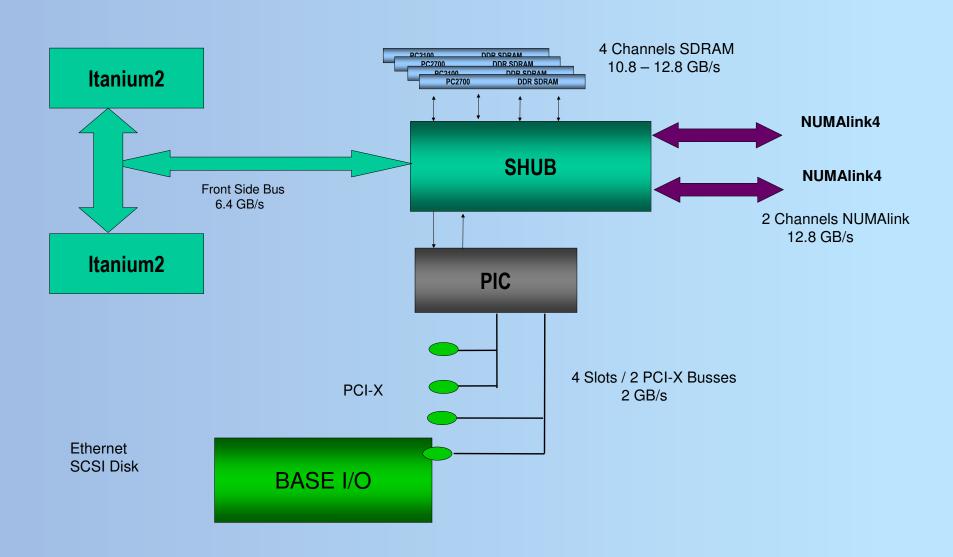

#### > Altix

- Modular aufgebaut (sog. Bricks + NUMAlink4)

- CR-Brick (4x Itanium-II Computing, Routing, Memory)

- SR-Brick (2x Virtex-4 FPGA Reconfigurable Computing)

- R-Brick (Routing)

- M-Brick (Memory)

- IX-Brick (I/O)

- D-Brick (Disk Storage)

- PA/PX-Brick (PCI(-X) Extensions)

- Verteilter Speicher mit gemeinsamen Adressraum

# SGI RASC Altix 350 CR-Brick

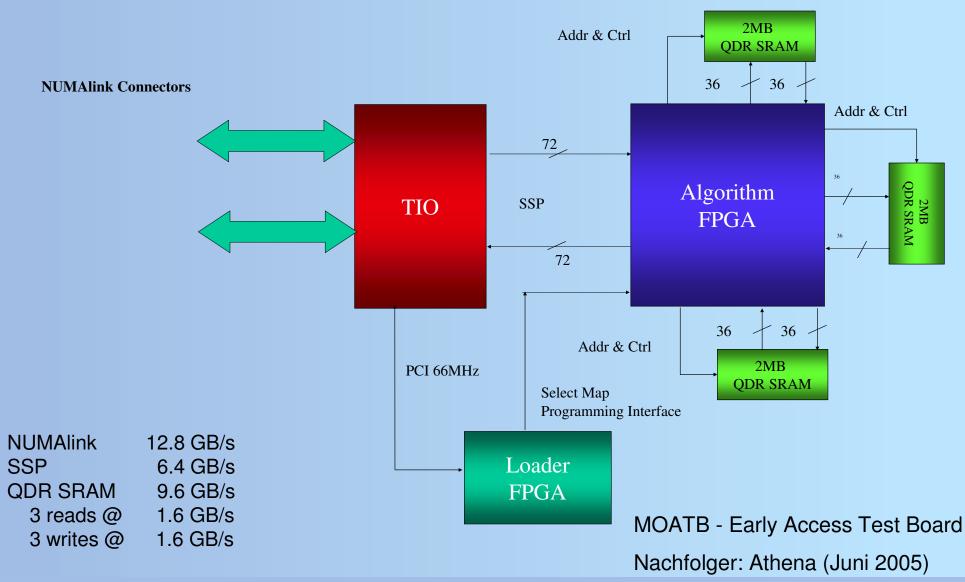

## Altix MOATB Blade

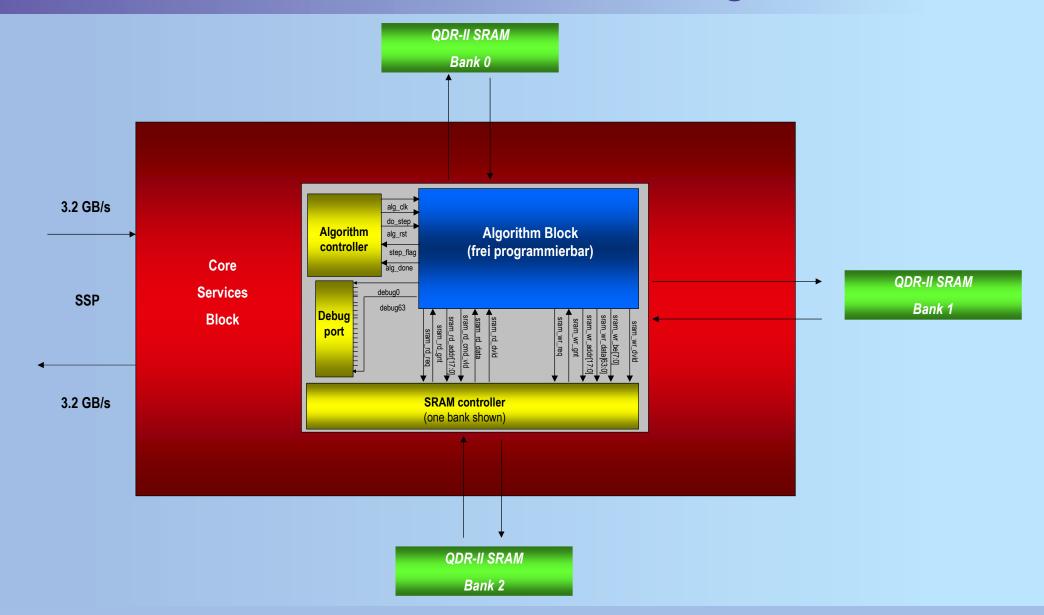

# SGI RASC Algorithmus-FPGA

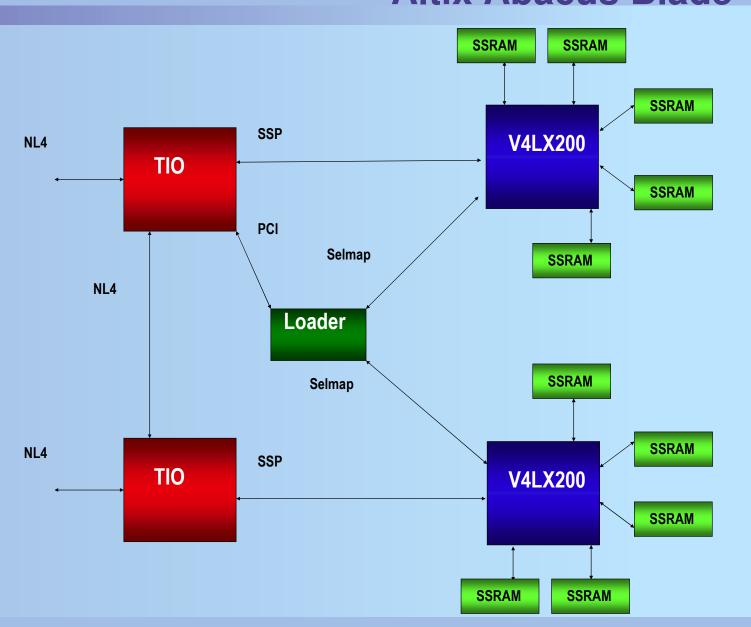

## SGI RASC Altix Abacus Blade

Release: Dezember 2005

TU Dresden bekommt 2 Stück im Frühjahr

### Potentielle Anwendungen

- > Bitmanipulation

- Kryptographie

- Vergleich von Gensequenzen (Bioinformatik)

- > Generieren von Zufallszahlen

- Monte-Carlo-Verfahren (Simulationsverfahren der Physik)

- Simulationsrechnungen z.B. Genetik

- Bildverarbeitung (fixed-point-arithmetik)

- Kantenerkennung, Mustererkennung, Bilderkennung (bewegt)

- (Video-)Transcoding, Kompression

- Seismische Daten, adaptive Optiken, Mikroskopbilder

- > Fast Fourier Transformation (fixed-point-arithmetik)

- Wissenschaftliches Rechnen

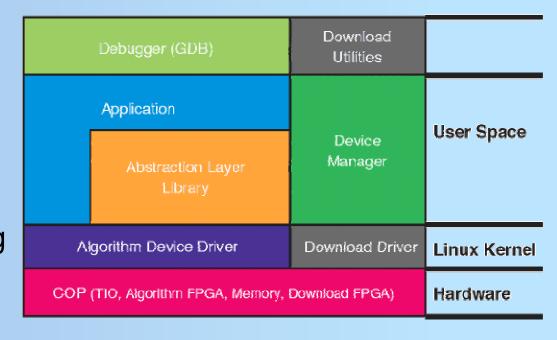

#### Softwareunterstützung

- > Programmiersoftware

- Celoxica, Impulse Acceleration, Mitrion, Viva

- > Debugger

- FPGA-erweiterete Version des GNU-Debuggers (GDB)

- > Vordefinierte HDL-Module

- Fertig optimiert

- Beispiele: ALU, FFT, häufige Algorithmen

- > RASC Abstraction Layer

- Siehe rechte Grafik

- Betriebssystemerweiterung

#### **Bestehende Probleme**

- > Wenige, sehr verschiedene Softwaretools

- Spezialwissen nötig

- > Entwicklung erfordert immer noch 3-fache Verifikation

- funktionale Simulation

- zeitliche Simulation

- Hardware-Test

- Diverse Hardwarekonfigurationen

- · z.B. Cray: Streaming-Prinzip mit mehreren FPGAs in Reihe

- sinnvollste Lösung muss ich noch durchsetzen

- > Anwendungen in der Testphase

- was sinnvoll ist und was nicht, muss sich noch zeigen

### Zukünftige Entwicklungen

- > Immer leistungsfähigere FPGAs

- > Einsatz auch im PC-Bereich

- Pläne existieren bereits

- > Verstärkter Einsatz im HPC

- Vereinheitlichung der Hardwarekonfigurationen

- Vereinheitlichung der Programmierung

- openFPGA-Initiative (http://www.openfpga.org/):

- OpenFPGA is an effort to bring together developers and hardware manufacturers, academic, government and commercial organizations to work together to advance the use of FPGA technology in high level applications. Collectively, OpenFPGA will foster shared and open efforts to address challenges of portability, interoperability and intra-application communication for FPGA and reconfigurable applications in highperformance and enterprise computing environments.

# Ausblick openFPGA

#### > Innovation

Verbreitung von Tools und Methoden zur Entwicklung von FPGA-basierten Programmen

#### Standardisierung

Definieren von Standards zur Kommunikation zwischen Programmen und FPGA-Hardware

#### > Ausbildung

Sammeln und Vorbereiten von Ausbildungsmaterial für zukünftige Anwender

#### > Förderung

- Unterstützung des FPGA-Einsatzes durch Dokumentieren erfolgreicher Anwendungen.

- > Kommunikation und Teilnahme an der Entwicklung

- > Rekonfigurierbares Computing mittels FPGAs

- Konzepte, Probleme, aktuelle Entwicklungen

Hardware: Rekonfiguration zur Laufzeit

Gleichberechtigung zu Mikroprozessoren

Software: Abstraktionsschichten des Betriebssystems

Mangelhafte Synthesetools

- > SGI Altix-Linie mit RASC-Blades

- Neuinstallation an der TU Dresden im Frühjahr 2006

- Passt ins Konzept (datenintensives Rechnen)

- sehr leistungsfähig, eventuell schwer zu beherrschen

- Fazit: Möglicherweise zukunftsweisend, auf jeden Fall enormes Potential!

#### Ende des Vortrags Schluß

> Danke für Ihre Aufmerksamkeit.

> Zeit für Fragen und Diskussion.

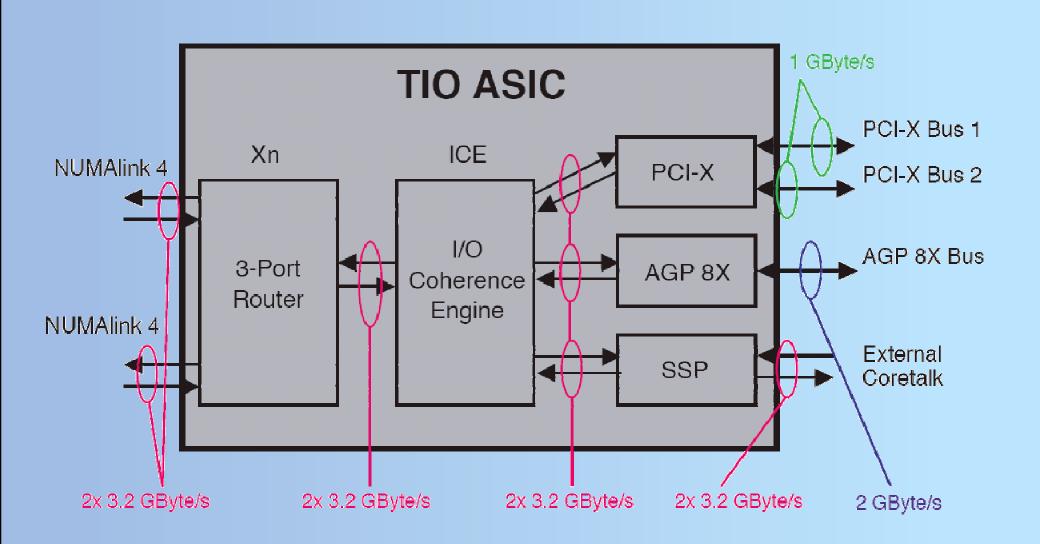

## Anhang TIO ASIC