# ASIC-SYNTHESE DER SHAP-MIKROARCHITEKTUR

Vortrag zum großen Beleg

Andrej Olunczek

Andrej.Olunczek@mailbox.tu-dresden.de

Dresden, 01.10.2008

## Gliederung

Einführung

Vergleich anderer Prozessoren

Realisierung

Zusammenfassung

## Einführung

### **Aufgabenstellung**

- Literaturstudium zu Flächenbedarf, Taktfrequenz und Leistungsaufnahme anderer eingebetteter Prozessoren

- Analyses des SHAP-VHDL-Designs und ggf. Entwurf/Generierung geeigneter Ersatzmodule mit Hilfe der Design-Tools

- Synthese des modifizierten Designs. Optimierung auf geringe Leistungsaufnahme und hohe Taktrate.

- Bestimmung der Kenndaten Chipfläche, erreichbare Taktfrequenz und Leistungsaufnahme in Abhänigkeit der Design-Parameter

- Zusammenfassung und Dokumentation der Ergebnisse.

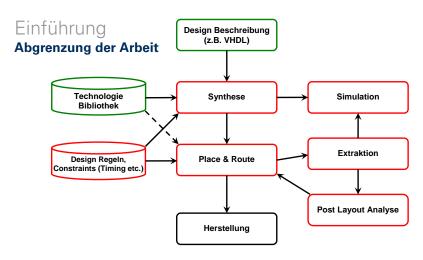

# Einführung

### **Motivation**

- Vergleich zu anderen eingebetteten Prozessoren

- Vergleich zu den FPGA-Implementierungen

- Abschätzung der Leistungsfähigkeit der Architektur

## Vergleich anderer Prozessoren

### Vergleich einiger Java-fähiger Prozessoren

| CPU            | aJile aj-100      | Fujitsu MB86799   | ARM926EJ-S                 |

|----------------|-------------------|-------------------|----------------------------|

| Architektur    | 32-bit Java Proz. | 32-bit Java Proz. | 32-bit RISC Proz.          |

|                | IEEE-754 FPU      | IEEE-754 FPU      | IEEE-754 FPU Coproz.       |

|                | nativ Java        | PicoJava-II       | Java-Coproz. (Jazelle)     |

|                | 32K Data Cache    | 8K Data Cache     | 8K Data Cache              |

|                | 16K Microcode     | 8K Instr. Cache   | 8K Instr. Cache            |

| Technologie    | $0.25 \mu m$      | $0.25 \mu m$      | 0.13μm                     |

| Takt           | 100 MHz           | 66 MHz            | 200 MHz                    |

| Benchmark      | 2,75 CM/MHz       | 9,4 CM/MHz        | 5 CM/MHz                   |

| emb. CM 3.0    |                   |                   |                            |

| Leistungsaufn. | 2,5 mW/Mhz        | 5,4 mW/Mhz        | 0,45 mW/Mhz                |

| Chipfläche     |                   |                   | 2.4 <i>mm</i> <sup>2</sup> |

# Vergleich anderer Prozessoren

### Vergleich Eckdaten in Abhänigkeit der Optimierung

Beispiel ARM Cortex-M3 (nur CM3Core)

- -- Takt optimiert nach Geschwindigkeit

- Takt optimiert nach Fläche

- -- Chipfläche optimiert nach Geschwindigkeit

- • Chipfläche optimiert nach Fläche

- --- Leistungsaufnahme optimiert nach Geschwindigkeit

- -- Leistungsaufnahme optimiert nach Fläche

## Vergleich anderer Prozessoren

### Vergleich Cachegrößen

#### Beispiel ARM9

| CPU     | Cache      | Techn.       | Takt    | Leistungsaufn. | Chipfläche                  |

|---------|------------|--------------|---------|----------------|-----------------------------|

| ARM920T | 2 * 16K    | 0.18 $\mu m$ | 200 MHz | 0,8 mW/MHz     | 11.8 <i>mm</i> <sup>2</sup> |

| ARM922T | 2 * 8K     | 0.18 $\mu m$ | 200 MHz | 0,8 mW/MHz     | 8.1 <i>mm</i> <sup>2</sup>  |

| ARM9    | ohne       | 0.18μm       | 200 MHz | 0,8 mW/MHz     | 4.4mm <sup>2</sup>          |

|         | (theoret.) |              |         |                |                             |

| ARM920T | 2 * 16K    | 0.13μm       | 250 MHz | 0,25 mW/MHz    | 4.7 <i>mm</i> <sup>2</sup>  |

| ARM922T | 2 * 8K     | 0.13μm       | 250 MHz | 0,25 mW/MHz    | 3.2 <i>mm</i> <sup>2</sup>  |

| ARM9    | ohne       | 0.13μm       | 250 MHz | 0,25 mW/MHz    | 1.7 <i>mm</i> <sup>2</sup>  |

|         | (theoret.) |              |         |                |                             |

## Vergleich anderer Prozessoren

#### Zusammenfassend

- geringere Strukturgröße ⇒ geringere Fläche und Leistungsaufnahme, höherer Takt

- Optimierung nach Geschwindigkeit ⇒ höhere Fläche, Leistungsaufnahme und Takt

- Optimierung nach Fläche ⇒ geringere Fläche, Leistungsaufnahme und Takt

- Cachegröße hat großen Einfluss auf die Chipfläche

### **Technologie**

- 0.13μm von UMC

- für Logik, 8 Metallisierungsebenen

- fsc0h\_d\_sc Faraday Standardzellenbibliothek

- Tools: 'Memaker' & 'Synopsys Design Compiler' & 'Cadence SOC'

#### **Arbeitsschritte**

- Analyse des Codes und Generierung Ersatzmodule ⇒ Erstellung von RAM-Makros ⇒ Optimierung der Makros nach gegebenen Punkten

- Hinzufügen der Padzellen, Synthese der Daten ⇒ Optimierung durch geeignete Bedingungen(Timing-constraints etc.) einstellen

- Place & Route in iterativen Schritten ⇒ Steuerung der Bedingungen, Lage der Makros und Padzellen, etc. durch Skripte

- Nach jeden Schritt Überprüfung der Einhaltung der Bedingung & Test durch Simulation

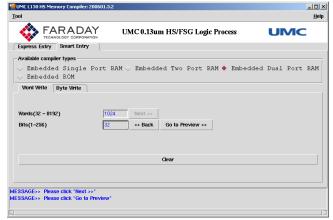

#### Memaker

#### Memaker

#### **Memaker Details**

• Auflistung möglicher Konfigurationen

| FSC0H_D_SJ (Sync. High Density DPRAM)                                                |       |                   |                      |                 |               |                |         |

|--------------------------------------------------------------------------------------|-------|-------------------|----------------------|-----------------|---------------|----------------|---------|

| Column Mux<br>(Aspect Ratio) Gate Count BC,TC,WC<br>loading=0.01pF<br>ckslew=0.016ns |       | DC Power<br>(uA)  | AC Power<br>(mA/MHz) | Area<br>(mm_sq) | Width<br>(um) | Height<br>(um) |         |

| 4 (1024x32x1)                                                                        | 65040 | 1.445,2.125,3.556 | 59.738               | 0.020           | 0.266         | 385.200        | 691.600 |

| 8 (1024x32x1)                                                                        | 62138 | 1.092,1.602,2.670 | 40.275               | 0.021           | 0.255         | 662.800        | 384.000 |

| 16 (1024x32x1)                                                                       | 71392 | 0.957,1.407,2.359 | 31.228               | 0.028           | 0.292         | 1202.400       | 243.200 |

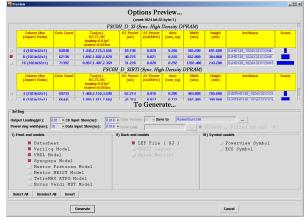

#### **Memaker Details**

- Auflistung möglicher Konfigurationen

- Auswahl guter Werte für eine hohe Taktrate

| FSC0H_D_SJ (Sync. High Density DPRAM)                                           |       |                   |                      |                 |               |                |         |  |

|---------------------------------------------------------------------------------|-------|-------------------|----------------------|-----------------|---------------|----------------|---------|--|

| Column Mux<br>(Aspect Ratio)  Gate Count BC,TC,WC loading=0.01pF ckslew=0.016ns |       | DC Power<br>(uA)  | AC Power<br>(mA/MHz) | Area<br>(mm_sq) | Width<br>(um) | Height<br>(um) |         |  |

| 4 (1024x32x1)                                                                   | 65040 | 1.445,2.125,3.556 | 59.738               | 0.020           | 0.266         | 385.200        | 691.600 |  |

| 8 (1024x32x1)                                                                   | 62138 | 1.092,1.602,2.670 | 40.275               | 0.021           | 0.255         | 662.800        | 384.000 |  |

| 16 (1024x32x1)                                                                  | 71392 | 0.957,1.407,2.359 | 31.228               | 0.028           | 0.292         | 1202.400       | 243.200 |  |

#### **Memaker Details**

- Auflistung möglicher Konfigurationen

- Auswahl guter Werte für eine hohe Taktrate

- Auswahl guter Werte für eine geringe Leistungsaufnahme

| $FSCOH\_D\_SJ$ (Sync. High Density DPRAM) |            |                                                         |                  |                      |                 |               |                |  |  |

|-------------------------------------------|------------|---------------------------------------------------------|------------------|----------------------|-----------------|---------------|----------------|--|--|

| Column Mux<br>(Aspect Ratio)              | Gate Count | Taa(ns)<br>BC,TC,WC<br>loading=0.01pF<br>ckslew=0.016ns | DC Power<br>(uA) | AC Power<br>(mA/MHz) | Area<br>(mm_sq) | Width<br>(um) | Height<br>(um) |  |  |

| 4 (1024x32x1)                             | 65040      | 1.445,2.125,3.556                                       | 59.738           | 0.020                | 0.266           | 385.200       | 691.600        |  |  |

| 8 (1024x32x1)                             | 62138      | 1.092,1.602,2.670                                       | 40.275           | 0.021                | 0.255           | 662.800       | 384.000        |  |  |

| 16 (1024x32x1)                            | 71392      | 0.957,1.407,2.359                                       | 31.228           | 0.028                | 0.292           | 1202.400      | 243.200        |  |  |

#### **Memaker Details**

- Auflistung möglicher Konfigurationen

- Auswahl guter Werte für eine hohe Taktrate

- Auswahl guter Werte f

ür eine geringe Leistungsaufnahme

- Festlegung auf eine Konfiguration für das zu nutzende RAM-Makro

| FSC0H_D_SJ (Sync. High Density DPRAM) |            |                                                         |                  |                      |                 |               |                |  |  |

|---------------------------------------|------------|---------------------------------------------------------|------------------|----------------------|-----------------|---------------|----------------|--|--|

| Column Mux<br>(Aspect Ratio)          | Gate Count | Taa(ns)<br>BC,TC,WC<br>loading=0.01pF<br>ckslew=0.016ns | DC Power<br>(uA) | AC Power<br>(mA/MHz) | Area<br>(mm_sq) | Width<br>(um) | Height<br>(um) |  |  |

| 4 (1024x32x1)                         | 65040      | 1.445,2.125,3.556                                       | 59.738           | 0.020                | 0.266           | 385.200       | 691.600        |  |  |

| 8 (1024x32x1)                         | 62138      | 1.092,1.602,2.670                                       | 40.275           | 0.021                | 0.255           | 662.800       | 384.000        |  |  |

| 16 (1024x32x1)                        | 71392      | 0.957,1.407,2.359                                       | 31.228           | 0.028                | 0.292           | 1202.400      | 243.200        |  |  |

### benötigte Speicher

| Speicher          | Taa(TC)  | aa(TC) DC Power AC Power |              | Area                         |

|-------------------|----------|--------------------------|--------------|------------------------------|

| Stack             | 2.230 ns | $65.529 \mu A$           | 0.025 mA/MHz | 0.453 <i>mm</i> <sup>2</sup> |

| Method Cache      | 1.291 ns | 26.813 <i>μA</i>         | 0.019 mA/MHz | 0.159 <i>mm</i> <sup>2</sup> |

| Garbage Collector | 0.995 ns | $12.451 \mu A$           | 0.010 mA/MHz | 0.052 <i>mm</i> <sup>2</sup> |

| Microtext         | 1.484 ns | $4.529\mu A$             | 0.004 mA/MHz | 0.033 <i>mm</i> <sup>2</sup> |

| Summe             | 2.230 ns | 109.322 <i>μA</i>        | 0.058 mA/MHz | 0.697 <i>mm</i> <sup>2</sup> |

# Zusammenfassung

- Kompromiss zwischen hoher Taktrate und niedriger Leistungsaufnahme finden

- gute Optimierungsmöglichkeiten schon bei der Generierung der RAM-Makros vorhanden

- Anpassung der RAM-Makros an die funktionalen Besonderheiten der FPGA-Implementierung

- Noch viel Arbeit im Bereich der Synthese und des Place & Route