Institut für Technische Informatik Professur für VLSI-Entwurfssysteme, Diagnostik und Architektur

# Optimierung rekonfigurierbarer Hardware mittels High-Level Synthese

Vortrag von Fabian Wendel im Rahmen des Proseminars Dresden // 05. Juli 2018

## **Gliederung**

#### Abkürzungsverzeichnis

#### **Motivation und Einleitung**

#### **Verwendete Plattform**

- Überblick

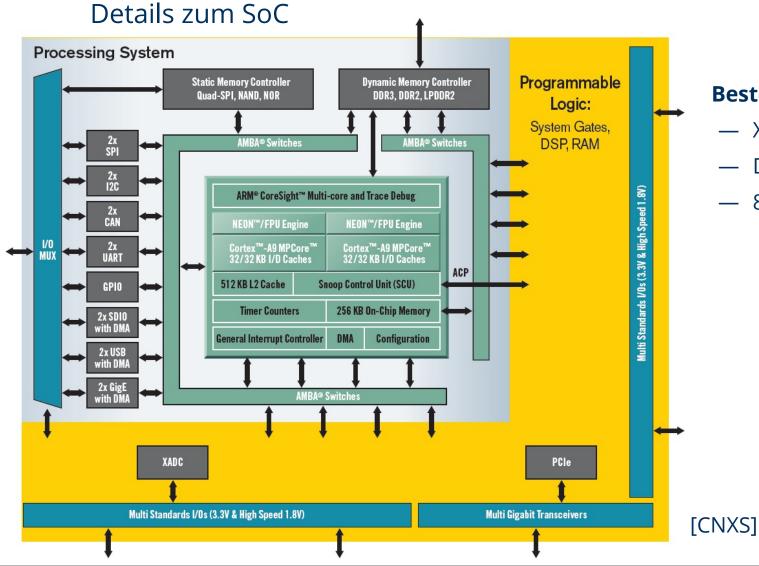

- Details zum SoC

#### **Verwendeter Algorithmus**

#### **High-Level Synthese (HLS)**

- Begriffsklärung

- Vivado HLS

- Direktive zur Leistungssteigerung

- Auswertung

#### **Fazit & Ausblick**

# Abkürzungsverzeichnis

**HLS** High-Level Synthese

**FPGA** Field Programmable Gate Array

**SoC** System on a Chip

**AP SoC** All Programmable SoC

**PL** Programmable Logic

**PS** Processing System

**RTL** Register Transfer Level

# Einleitung

## **Motivation & Einleitung**

Warum & Wie?

#### **Rekonfigurierbare Hardware**

- Relevanz im Architekturdesign

- Löst Grenzen auf

- Flexibilität

- Entwurf per Hand umständlich

### **Lösung: Automatisierter Systementwurf mittels HLS:** Software → Hardware

#### Thema dieser Arbeit

- Verschiedene Möglichkeiten der Leistungssteigerung

- Auswertung nach Effizienz

# **Verwendete Plattform**

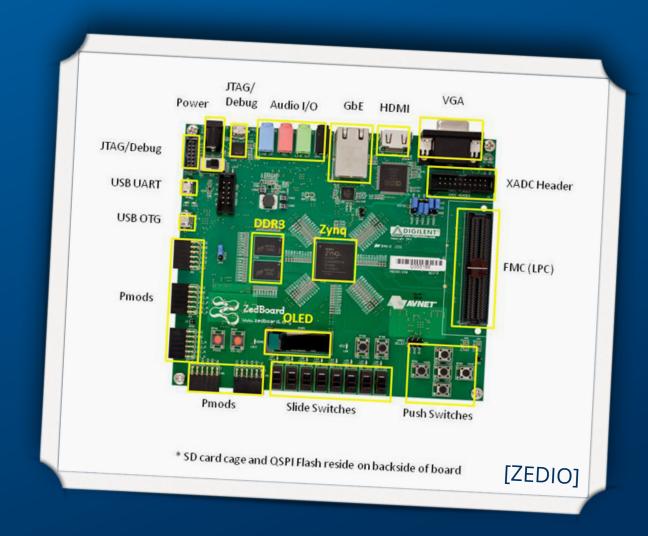

#### **Verwendete Plattform**

#### Überblick

#### **Zum Board**

— Boardname: "ZedBoard"

Hersteller: AVNET

Einsatzbereich: Schnelles Prototyping, Machbarkeit

#### **Spezifikationen**

SoC: Zynq-7000 AP SoC XC7Z020-CLG484-1

Arbeitsspeicher: 512MB DDR3

— ROM: 4GB SD-Karte

— Kommunikation: USB-JTAG, USB-UART, Ethernet

Anzeige: 128x32 OLED Display, VGA- & HDMI-Ausgang

Taktgeber: 33.333 MHz Processing System (PS),

100MHz Programmable Logic (PL)

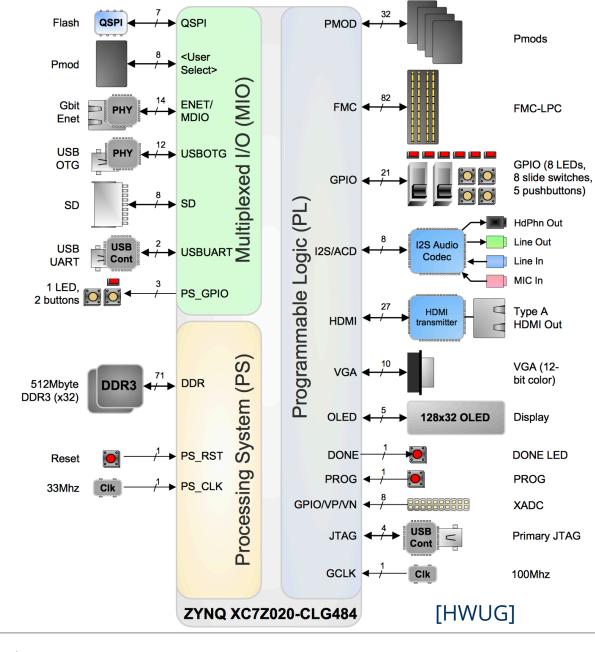

#### **Verwendete Plattform**

#### **Besteht aus**

- Xilinx Zynq-7000 All Programmable SoC (AP SoC)

- Dual Cortex-A9 PS

- 85.000 Series-7 PL Zellen

# **Verwendeter Algorithmus**

# **Verwendeter Algorithmus**

# Matrixmultiplikation

#### **Warum Matrixmultiplikation**

- Bekannte Rechenoperation

- Geringe Komplexität → einfach nachzuvollziehen

#### **Algorithmus**

— Einzelne Einträge:

$$c_{ik} = \sum_{j=1}^{m} a_{ij} \cdot b_{jk}$$

```

#include "matrixmul.h"

void matrixmul.h"

wide matrixmul.h"

mat_at_at_a|MMT_A_ROWS|[MAT_A_COLS].

mat_bt_b|MMT_B_ROWS|[MAT_B_COLS].

result_t res[MAT_A_ROWS][MAT_B_COLS]

{

// Iterate over the rows of the A matrix

Row: for(int i = 0: i < MAT_A_ROWS: i++) {

// Iterate over the columns of the B matrix

Col: for(int j = 0: j < MAT_B_COLS: j++) {

// Do the inner product of a row of A and col of B rows of the Inner product of a row of A and col of B rows of A sand col of B res[i][j] += a[i][k] * b[k][j]:

}

}

}

```

# Begriffsklärung

#### Nutzen

- Rechnergestützt

- Algorithmische Schaltungsfunktionen

- → Register-Transfer-Struktur

#### **Funktionsweise**

Operationen werden zu arithmetisch/ Logischen Funktionseinheiten zusammengefasst

|    | Operation\Control Step | C0 | C1 | C2 | C3 | C4 |

|----|------------------------|----|----|----|----|----|

| 1  | ⊡Row                   |    |    |    |    |    |

| 2  | i(phi mux)             |    |    |    |    |    |

| 3  | exitcond2(icmp)        |    |    |    |    |    |

| 4  | i 1(+)                 |    |    |    |    |    |

| 5  | tmp s(-)               |    |    |    |    |    |

| 6  | ⊟Col                   |    |    |    |    |    |

| 7  | j(phi mux)             |    |    |    |    |    |

| 8  | exitcond1(icmp)        |    |    |    |    |    |

| 9  | j 1(+)                 |    |    |    |    |    |

| 10 | tmp 2(+)               |    |    |    |    |    |

| 11 | ⊡Product               |    |    |    |    |    |

| 12 | res load(phi mux)      |    |    |    |    |    |

| 13 | k(phi mux)             |    |    |    |    |    |

| 14 | node 40(write)         |    |    |    |    |    |

| 15 | exitcond(icmp)         |    |    |    |    |    |

| 16 | k 1(+)                 |    |    |    |    |    |

| 17 | tmp 4(+)               |    |    |    |    |    |

| 18 | tmp 11(-)              |    |    |    |    |    |

| 19 | tmp 12(+)              |    |    |    |    |    |

| 20 | a load(read)           |    |    |    |    |    |

| 21 | b load(read)           |    |    |    |    |    |

| 22 | tmp 7(*)               |    |    |    |    |    |

| 23 | tmp 8(+)               |    |    |    |    |    |

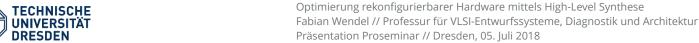

#### Vivado HLS

#### **Ablaufplan des Programms**

**A. C-Simulation**: Syntaxcheck des Algorithmus

**B. Debugging**: Verifikation des Testcodes

**C. C-Synthese**: Bauen des RTL-Designs

**D. Analyse**: Untersuchen des Designverhaltens

**E. C/RTL-Cosimulation**: Verifikation des RTL-Designs

**F. RTL exportieren**: Ausgabe des RTL-Codes

#### Für Auswertung

Fokus auf Punkte C. und D.

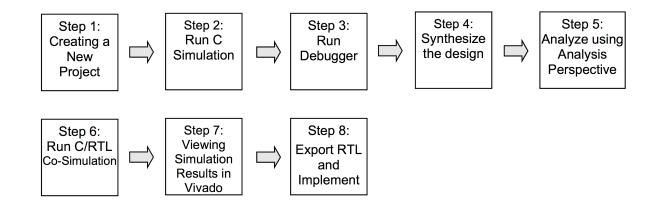

### Pipelining zur Leistungssteigerung

#### **Warum Pipelining**

- Allgemein bekannt

- Signifikante Beschleunigung

#### **Mehre Optionen zur Positionierung**

- Äußere Schleife (Iteration über Zeilen)

- Mittlere Schleife (Iteration über Spalten)

- Innerste Schleife (Multiplikation und Summation der einzelnen Einträge)

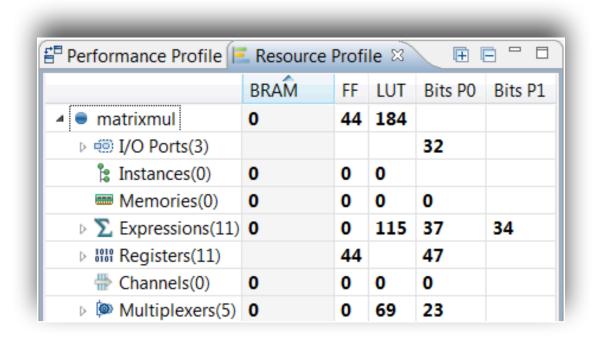

Auswertung (Zahlen)

#### **Taktdauer**

$8,7 \text{ ns} < 10 \text{ns} \Rightarrow \text{realisierbar}$

#### Latenz

- Umso weiter außen, desto geringer

- Grund: je mehr Unrolling, desto mehr Parallelisierung

| Bewertungskriterium       |       |          |          |          |

|---------------------------|-------|----------|----------|----------|

| /gepipelinete Schleife    | Keine | Innerste | Mittlere | Äußerste |

| Erreichbare Taktdauer/ns  | 8,7   | 8,7      | 8,7      | 8,7      |

| Latenz/Taktzyklen         | 79    | 91       | 22       | 18       |

| Gesamtbearbeitungszeit/ns | 687,3 | 791,7    | 191,4    | 156,6    |

| Beschleunigung            | 1     | 0,87     | 3,59     | 4,39     |

| DSP48E                    | 1     | 1        | 2        | 6        |

| FF                        | 44    | 56       | 85       | 484      |

| LUT                       | 184   | 277      | 325      | 393      |

#### Gesamtbearbeitungsdauer

- Erwartete Taktdauer \* Anzahl Taktzyklen⇒ proportional zur Latenz

- Beschleunigung: Mittlere > 3; Äußere > 4

#### Ressourcen

- Aufwand steigt mit Bearbeitungsgeschwindigkeit

- Jedoch nie mehr als zweiprozentige Auslastung

Auswertung (Diagramm)

# **Fazit & Ausblick**

#### **Fazit & Ausblick**

#### Rückschlüsse aus der Arbeit

#### **Fazit**

- HLS als effizientes Mittel im Architekturentwurf

- Entwicklungszeit wird reduziert

- Berechnung wird beschleunigt

#### Ausblick auf zukünftige Forschungsthemen

- Verwendung anderer Direktiven als Pipelining zur Beschleunigung?

- Ressourcenabhängige Begrenzung der Effizienz von HLS?

Amazon Web Services, Inc. [Ama18]

# Quellen

## Quellen

#### **Abbildungen**

[AVERZ] **mystipendium.de.** "Idee" In: <a href="https://www.mystipendium.de/studium/einleitung-">https://www.mystipendium.de/studium/einleitung-</a>

hausarbeit, Online 04.07.18.

[IDEE] thesius. "Das Abkürzungsverzeichnis in der Bachelorarbeit" In: https://www.thesius.de/

blog/articles/abkuerzungsverzeichnis/, Online 04.07.18.

[ZEDIO] **zedboard.org.** "Functional Overlay" In: <a href="http://zedboard.org/product/zedboard">http://zedboard.org/product/zedboard</a>, Online

22.06.18.

[CNXS] CNXSOFT. "Xilinx Zynq-7000 EPP Block Diagram" In: https://www.cnx-software.com/

2012/03/29/xilinx-zynq-7000-extensible-processing-platform-epp-dual-cortex-a9-fpga-

soc/, Online 05.07.18

#### **Dokumente**

[HWUG] **Xilinx Inc.** *ZedBoard (Zyng Evaluation and Development)*

Hardware User's Guide. ZedBoard\_HW\_UG (v2.2), 02.07.18

[XILL1] Xilinx Inc. Vivado HLS Design Flow Lab. 01\_Lab1, 13.06.18

# Vielen Dank für eure Aufmerksamkeit! Fragen?