Kommunikationsinfrastrukturen für Attonetze in 3D Chipstapeln

Motivation und Ziel

Die fortwährende Miniaturisierung führt in den nächsten 20 Jahren an physikalische Grenzen. Bereits heute werden Chips in 14 nm CMOS produziert. Bei weiterer Skalierung sind die Abstände der Transistorgeometrien in der Größenordnung weniger Siliziumatome im Kristallgitter bzw. nur noch wenige Atomlagen dünn.

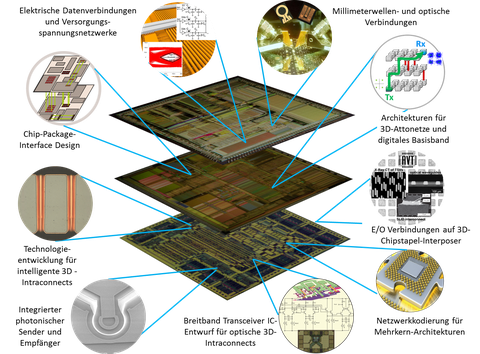

Ein möglicher Ausweg ist die 3D-Integration, d.h. das Stapeln von Chips übereinander. Hierdurch entstehen im Miniaturformat „Hochhäuser“ der Elektronik. Um das gesamte Potential dieser Technologie nutzen zu können, ist es notwendig, dass Informationen innerhalb des gesamten Chipstapels ausgetauscht werden können. Dies bedeutet, dass eine völlig neue Kommunikationsinfrastruktur mit all ihren Komponenten in kleinsten Abmessungen erforscht und entworfen werden muss, die hochgradig energieeffizient und ressourcenschonend ist. Durch diese Kommunikationsinfrastruktur entsteht ein eigenes Internet innerhalb eines Chipstapels im Kleinstformat, weshalb dies für die neue Forschergruppe „3D-Attonetz“ genannt wird.

Das Thema dieser Nachwuchsforschergruppe gehört zu einer der wichtigsten Branchen Sachsens und Deutschlands (vgl. auch Hightech-Strategie des Bundes und Innovationsstrategie des Freistaates Sachsen), der Informations- und Kommunikationstechnologie. Die Mikroelektronik-, Halbleiter- und Photovoltaikindustrie hat eine lange Tradition im Raum Dresden/Freiberg/Chemnitz. Das sächsische Forschungs- und Entwicklungscluster Silicon Saxony, das ca. 300 Mitgliedsfirmen zählt, in denen etwa 40.000 Menschen beschäftigt sind, hat diese Bedeutung erkannt und treibt das Zukunftsthema 3D-Integration ebenfalls stark voran.

Die 3D-Integration und darauf aufbauend die 3D-Attonetze werden als Schlüsseltechnologie für viele zukünftige Produkte, innovative Technologien und Megatrends wie Smart Cities, Smart Grids oder Industrie 4.0 gesehen. Darunter z.B. auch das Taktile Internet, welches zusammen mit der fünften Mobilfunkgeneration ab ca. 2022 seinen Marktstart haben wird.

Beteiligte Professoren

Prof. Johann W. Bartha, Institut für Halbleiter- und Mikrosystemtechnik, Professur Halbleitertechnik

Prof. Karlheinz Bock, Institut für Aufbau- und Verbindungstechnik

Prof. Frank Ellinger, Lehrstuhl für Schaltungstechnik und Netzwerktheorie

Prof. Gerhard Fettweis, Vodafone Stiftungslehrstuhl Mobile Nachrichtensysteme

Prof. Frank Fitzek, Deutsche Telekom Chair for Communication Networks

Jun.-Prof. Kambiz Jamshidi, Lehrstuhl Hochfrequenztechnik

Prof. Jens Lienig, Institut für Feinwerktechnik und Elektronik-Design

Prof. Christian Mayr, Stiftungsprofessur für Hochparallele VLSI-Systeme und Neuromikroelektronik

Prof. Dirk Plettemeier, Lehrstuhl Hochfrequenztechnik

Projektlaufzeit

01.09.2015 - 31.08.2018

01.09.2018 - 28.02.2019

Projektfinanzierung

Finanziert aus Mitteln der Europäischen Union und des Freistaates Sachsen.