IC designs 2016 - 2020

Table of contents

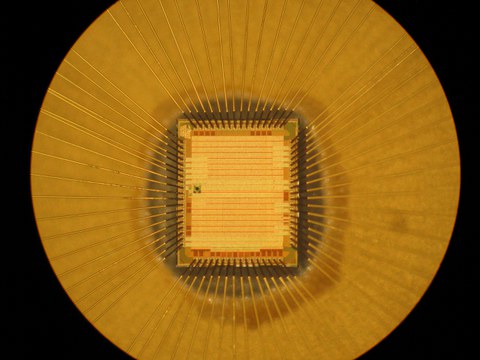

AUTOLINK_28

Autolink28 is an Ethernet physical layer test chip 1000BASE-T1 Ethernet standard. It contains physical coding sublayer (PCS) and physical medium attachment (PMA) on TX and RX, respectively, and reaches a symbol rate upto 750 Mbps with full duplex mode.

Chipfoto Autlink_28-IC

| Technology | 28 nm CMOS |

| Area | 2,75 mm² |

| Tape-Out | 09_2016 |

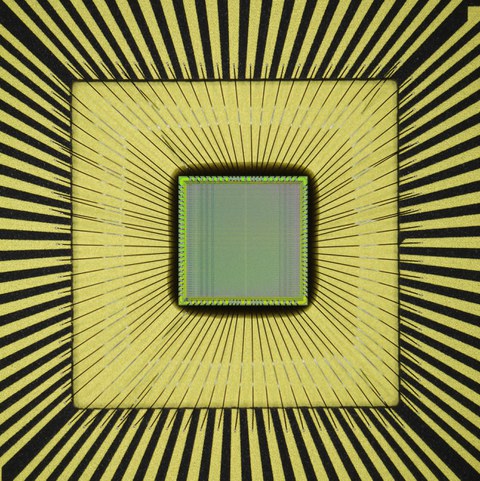

JIB_1

JIB1 is the first prototype of the quad processing unit (QPE) architecture and layout for the SpiNNaker2 chip. JIB1 contains two QPEs, so a total of 8 processing elements. Each processing element has a multiply-accumulate array for deep neural networks, log, exp and random function generators for spiking neural networks, and an ARM M4F core. All numerical units incorporate dynamic voltage and frequency scaling, i.e. energy and clock frequency scale with the compute activity of the chip. The chip contains other system components for the final SpiNNaker2 chip, such as the updated SpiNNaker router, a DMA engine, custom high-speed on- and off-chip communication links, etc.

Chipfoto JIB1-IC

| Technology | 22 nm FDSOI |

| Area | 9 mm² |

| Tape-Out |

03_2018 |

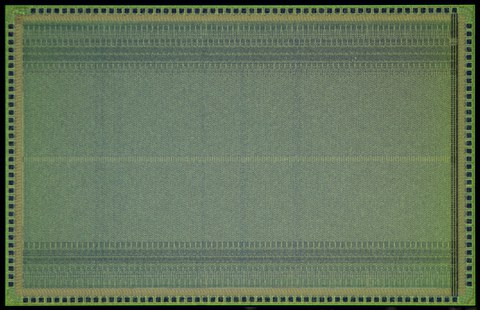

Kachel

Coorperation with MNS, MPSoC with 4 cores and fine-grained power management. Single-ended 2GBit/s/lane chip-to-chip links to extend NoC to neighbouring chips.

Chipfoto Kachel-IC

| Technology | 22 nm FDSOI |

| Area | 8,4 mm² |

| Tape-Out |

05_2018 |

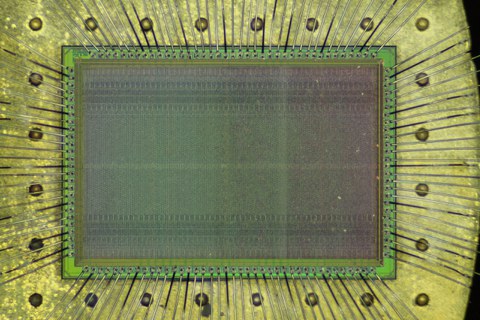

Kachel_2

Coorperation with MNS, MPSoC with 11 cores and fine-grained power management. Single-ended 2GBit/s/lane chip-to-chip links to extend NoC to neighbouring chips.

Chipfoto Kachel2-IC

| Technology | 22 nm FDSOI |

| Area | 14,5 mm² |

| Tape-Out |

02_2019 |

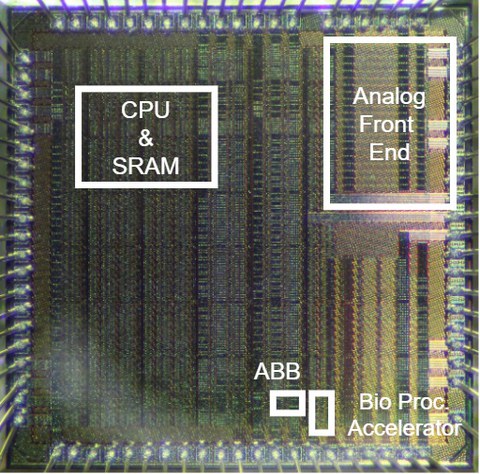

GEPARD

Smart neural SoC including MAC-assisted CPU, 16-Ch AFE, bio-processing accelerator, and ABB unit. The proposed SoC achieves an average classification accuracy of 94.12% and power consumption of 2.79μW/Ch for the classification and 1.52μW/Ch for the AFE. Various architecture- and circuit-level techniques are deployed to achieve the ultra-low-power operation.

Chipfoto GEPARD-IC

| Technology | 22 nm FDSOI |

| Area | 4 mm² |

| Tape-Out |

06_2019 |

| Publications |

"DOI: 10.1109/TCSII.2021.3121034 |

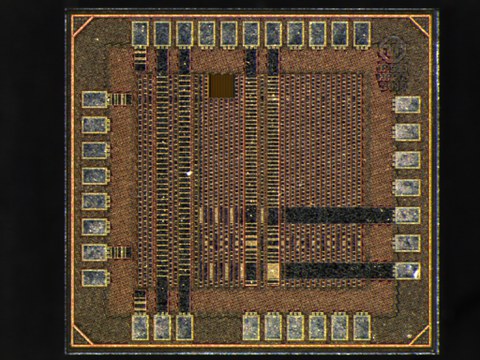

IPCEI_ADC-test

Test chip of a dual ADC macro for the IPCEI Radar DSP.The dual ADC macro contains 2 SAR ADCs with 12 bit resolution and 28 MSamples/s used for synchronous sampling of I and Q components of the IF signals from the radar frontend.

Chipfoto IPCEi ADC-Test-IC

| Technology | 22 nm FDSOI |

| Area | 1,56 mm² |

| Tape-Out |

08_2019 |

JIB_2

JIB2 is the second (and final) prototype of the quad processing unit (QPE) architecture and layout for the SpiNNaker2 chip. Its goal is to silicon-verify all the macros in their final layouts that will compose SpiNNaker2. Thus, it contains the final versions of the QPEs with all machine learning and neuromorphic functionality described for JIB1, plus the layouts of the LPDDR4 interfaces. It is also intended to test the final package and interposer design, so it is actually house in the same package as SpiNNaker2. JIB2 contains: 2 QPEs (i.e. 8 PEs), Chip2chip links, Board2Board links, Ethernet host interface, the final SpiNNaker2 event router, etc. Fun fact: in the picture, the mirror-like element in the middle is actually the backside of the JIB2 die, i.e. the silicon chip itself. In this package, the backside of the die sticks up out of the upper side.

Chipfoto JIB2-IC (BGA-Package)

| Technology | 22 nm FDSOI |

| Area | 19,8 mm² |

| Tape-Out |

03_2020 |

| supported by the European Union 7th and Horizon-2020 Framework Programmes, under grant agreements 720270, 785907 (HBP) |

|

| <- 2011 - 2015 |