IC designs 2005 and earlier

Table of contents

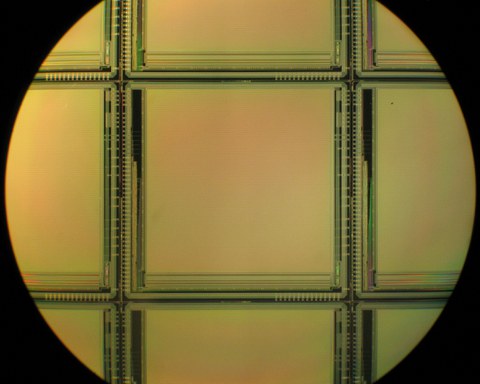

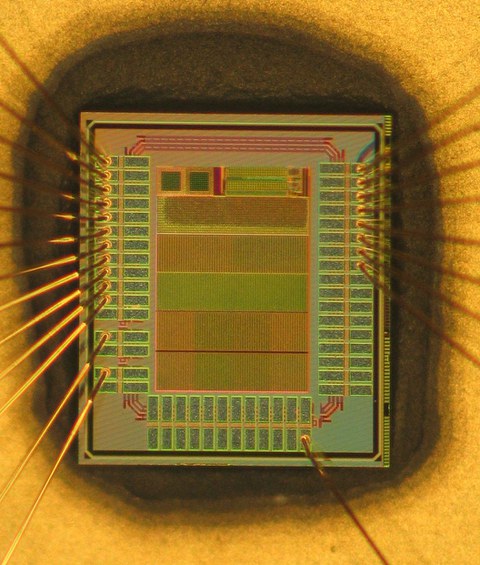

N128

Image sensor coupled to a analog neural preprocessing unit. Array of 128x128 McCulloch Pitts neurons with nearest-neighbor coupling, enabling preprocessing like diffusion, binarisation and segmentation.

N128, Chipfoto, Wafer-Ausschnitt

| Technology | 1,0 µm CMOS |

| Area | 233 mm² |

| Tape-out | 01_1997 |

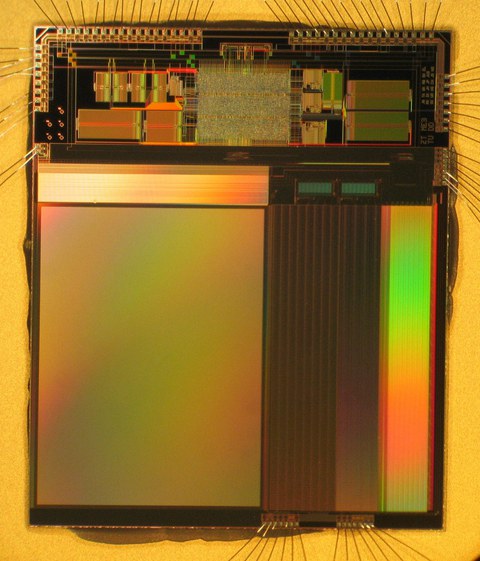

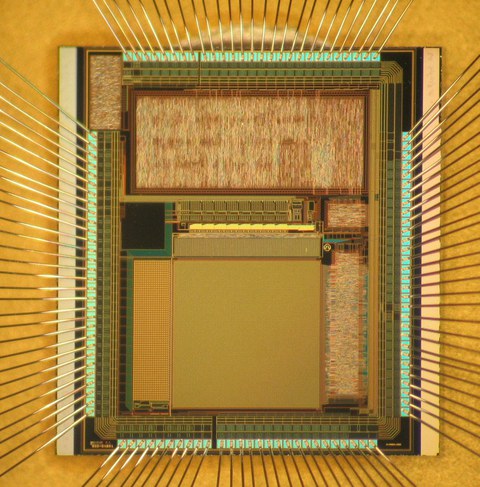

1-CHIP CMOS-CAMERA

Image sensor coupled to on-chip digital signal processing unit. The image can be preprocessed to automatically correct gamma, fixed-pattern noise and defect pixels.

Chipfoto 1-Chip CMOS-Camera

| Technology | 0,6 µm CMOS |

| Area | 111 mm² |

| Tape-Out | 01_1998 |

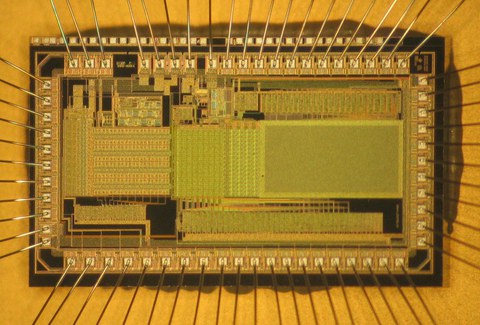

VISP 128

Visual Instruction Sensor Processor (VISP):

Analog Processor for 8x8 Matrix Multiplications (as in JPEG). Focal plane operation,

demonstrator imager with 64x128 Pixels. Analog pixel data is multiplied with digital

coefficients by digitally controlling the current paths in the analog processor.

A computational ADC performs binary weighted sum in a error-correcting current mode ADC. The analog processor is sufficient for JPEG compression with good quality.

The concept is fast enough to be scaled to 720 lines / 30 fps.

Chipfoto VISP 128

| Technology | 0,6 µm CMOS |

| Area | 11,25 mm² |

| Tape-Out | 02_2002 |

AMS-Neuro

Array of 4096 spiking neurons with nearest-neighbor coupling via adaptive Hebbian synapses. Used for image segmentation, with areas of similar gray scale values resulting in a wave-like synchronization.

Chipfoto AMS-Neuro

| Technology | 0,35 µm CMOS |

| Area | 42,25 mm² |

| Tape-Out | 05_2003 |

Vision_IC Neuro

Mixed-signal processor for 128x128 analog image feature detection. Pixels are processed by a nearest-neighbor integrate-and-fire neural network with adaptive Hebbian synapses. Also used as a test chip for 3D connection technology.

Chipfoto Vision_IC

| Technology | 130 nm CMOS |

| Area | 50 mm² |

| Tape-Out | 07_2003 |

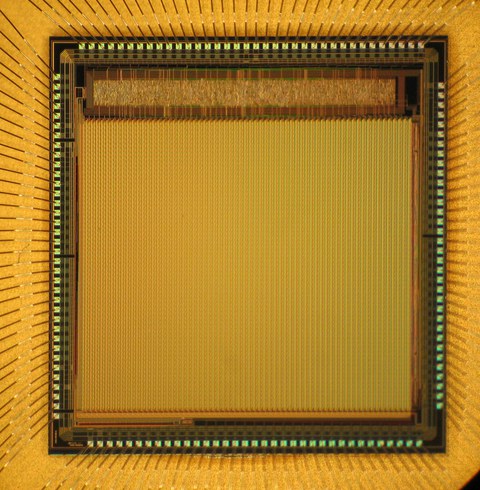

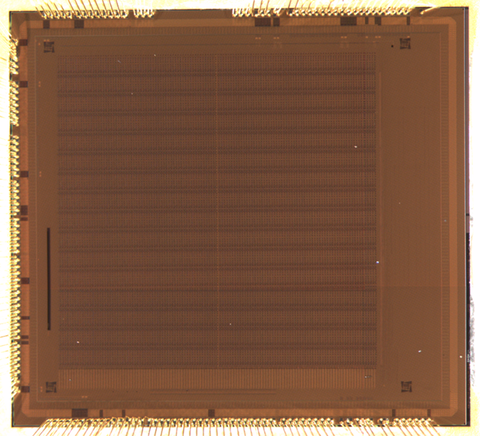

Active-Pixel-Sensor

Active sub-100nm pixel image sensor to test structures in varying depths in the substrate, establishing different spectral sensitivity. This enables color processing without a color mask.

Chipfotos APS 90

| Technology | 90 nm CMOS |

| Area | 2,56 mm² |

| Tape-Out | 07_2003 |

High Speed CMOS Sensor (HSCS)

128*128 pixel 300 FPS high-speed image sensor with digital feature processing (binarization and object tracking). Also used as a test chip for an ADPLL.

Chipfoto HSCS-IC

| Technology | 0,35 µm CMOS |

| Area | 10,5 mm² |

| Tape-Out | 12_2003 |

Vision_IC CCam

16384 digital pulse computation and routing cells, mimicking neural microcircuits. Pulsing pixels in each cell provide optical input. The overall chip enables neural-microcircuit-like image convolution similar to visual cortex

Chipfoto Vision_IC CCam

| Technology | 130 nm CMOS |

| Area | 50 mm² |

| Tape-Out | 11_2004 |

| Publication | https://ieeexplore.ieee.org/stamp/stamp.jsp?arnumber=4182396 |

| 2006 -2010 -> |