08.10.2018

TSV Transistor—Vertical Metal Gate FET Inside a Through Silicon Via

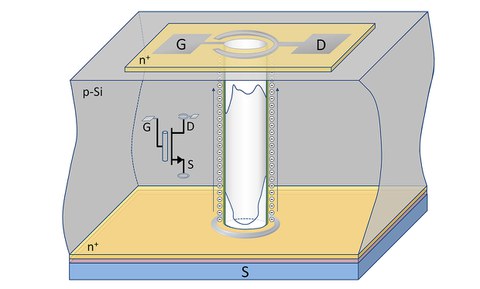

Schematic of the IHM TSV transistor (Felix Winkler/University of Dresden/IEEE Electron Device Letters)

Ein im Institut für Halbleiter- und Mikrosystemtechnik entwickelter TSV Transistor - Vertical Metal Gate FET Inside a Through Silicon Via (siehe Abstract) wurde mit viel positivem Feedback im Journal IEEE Electron Device Letters veröffentlicht. Im IEEE Spectrum wurde dem Paper ein eigener Beitrag gewidmet: Through-Silicon Transistors Could Make Stacking Chips Smarter

Abstract

A new vertical field-effect transistor (FET) has been fabricated inside a through silicon VIA (TSV). Front side and backside of a 200 μm thin p-doped Si wafer were highly n-doped to shape the source/drain areas of the FET. The lateral surface of the TSV forms the channel with a length of 200μm (wafer thickness) and a width of 63μm (circumference of the 20- μm hole). A stack of SiO2 and Al2O3 was used as gate dielectric material and Ru/TaN/Ru was deposited as gate metal using atomic layer deposition. The n-channel TSVFETs showed saturation currents of 150 μA for a gate voltage of 4 V and an ON/OFF current ratio of about 104.