Leistungs- und Energieeffizienz-Analyse für innovative Rechnerarchitekturen

Über die Leistungsfähigkeit von Prozessoren und Systemen hinausgehend zeigt sich seit mehreren Jahren, dass eine weitere wissenschaftliche Schwerpunktsetzung in Bezug auf Energieeffizienz von Rechnersystemen unbedingt erforderlich ist. Die Effizienzsteigerungen durch verbesserte Fertigungsverfahren sinken zunehmend und müssen durch breiter verankerte Maßnahmen verstärkt werden. Hier zeigt sich, dass die Optimierung paralleler Anwendungen hinsichtlich ihrer Energieeffizienz vielversprechend ist – insbesondere durch eine intelligente Steuerung der unterliegenden Hardware durch die wissenschaftlichen Anwendungen.

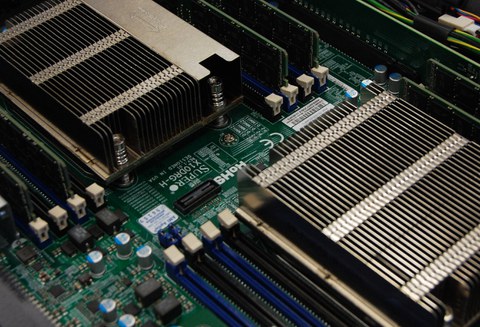

Einen weiteren Forschungsschwerpunkt hinsichtlich neuartiger Rechnerarchitekturen stellen Hardwarebeschleuniger dar, die inzwischen hauptsächlich durch sogenannte general purpose GPUs (GPGPUs) sowie manycore-Prozessoren vertreten werden. Die Forschungsarbeiten am ZIH auf diesem Gebiet reichen von der detaillierten Untersuchung der Hardware-Beschleuniger über die Bereitstellung von Software-Werkzeugen für die Performance-Analyse bis hin zur Portierung und Optimierung von wissenschaftlichen Anwendungen auf Beschleuniger-Architekturen.

Aktuelle Projekte

- SEANERGYS: Software for Efficient and Energy-Aware Supercomputers

- IT-Zauber: Integrale Transformation – Zwilling zur Ausbauplanung, Umsetzung und Betriebsoptimierung energieeffizienter Rechenzentren

- EECliPs: Energieeffiziente Klimasimulationen auf heterogenen Supercomputern durch Co-Design

- FIRESTARTER: Ein Werkzeug zum Erzeugen von maximaler Leistungsaufnahme von Prozessoren

- lo2s: leichtgewichtiges Linux-Performance-Monitoring

-

SPEC: Standard Performance Evaluation Cooperation

-

BenchIT: Flexible und portable Performance-Analyse für Rechnersysteme

- Dresden GPU Center of Excellence

- cfAED: Center For Advancing Electronics Dresden

- HDEEM: High Definition Energy Efficiency Monitoring

- HAEC: Highly Adaptive, Energy Efficient Computing

- READEX: Runtime Exploitation of Application Dynamism for Energy-Efficient Exascale Computing

- Score-E: Skalierbare Werkzeuge zur Energieanalyse und -optimierung im Höchstleistungsrechnen

- Cool Silicon: Energy Efficiency Innovations from Silicon Saxony

- HI-CFD / Scout: Hocheffiziente Implementierung von CFD-Codes für HPC-Many-Core-Architekturen

- SIOX: Skalierbare Infrastruktur zur automatischen Leistungsanalyse paralleler Codes

- GASPI: Global Address Space Programming Interface

- eeClust: Energieeffizientes Cluster-Computing

- Fast Matrix Multiplication on Cell (SMP) Systems

- Software Tracing on Cell/B.E. Processors

- EP-Cache

- PARbench

© Sven Ellger

© Sven Ellger

Dr. Daniel Hackenberg

Stellvertretender Direktor / Gruppenleiter Energieeffizienz

Eine verschlüsselte E-Mail über das SecureMail-Portal versenden (nur für TUD-externe Personen).

Zentrum für Informationsdienste und Hochleistungsrechnen (ZIH)

Zentrum für Informationsdienste und Hochleistungsrechnen (ZIH)

Besucheradresse:

Willers-Bau, Raum A 204 Zellescher Weg 12

01069 Dresden

None

Ausgewählte Publikationen

-

Christian von Elm and Robert Schöne. "Performance Tools for the NEC SX-Aurora Tsubasa". In Companion of the 16th ACM/SPEC International Conference on Performance Engineering (ICPE Companion ’25). DOI: 10.1145/3680256.3721323

-

Malte-Christian Kuns, Hannes Tröpgen, Robert Schöne, "An Analysis of User-space Idle State Instructions on x86 Processors" Proceedings of the 16th ACM/SPEC International Conference on Performance Engineering (ICPE '25), DOI: 10.1145/3676151.3719370

-

Christian von Elm, Sebastian Oeste, Mario Bielert, Thomas Ilsche. "Augmenting HPC I/O Performance Analysis with Detailed Block Layer Insights", In: IPTW Dresden 2025 (accepted for publication)

-

Cyrill Burth, Markus Velten, Robert Schöne. "Introducing the Arm-membench Throughput Benchmark", In: International Conference on Parallel Processing and Applied Mathematics (PPAM '24), DOI: 10.1007/978-3-031-85697-6_7

-

Thomas Ilsche, Sebastian Schrader, Robert Schöne. "Optimizing Idle Power of HPC Systems: Practical Insights and Methods" In: IEEE International Conference on Cluster Computing Workshops (CLUSTER Workshops 2024). DOI: 10.1109/CLUSTERWorkshops61563.2024.00014

-

Hannes Tröpgen, Robert Schöne, Thomas Ilsche, Daniel Hackenberg. "16 Years of SPEC Power: An Analysis of x86 Energy Efficiency Trends" In: IEEE International Conference on Cluster Computing Workshops (CLUSTER Workshops 2024). DOI: 10.1109/CLUSTERWorkshops61563.2024.00020

-

Christian Wassermann, Mario Bielert, Gert Vanberg, Daniel Hackenberg, Christian Terboven, Matthias S. Müller. "Calculating User-Centric Carbon Footprints for HPC" In: IEEE International Conference on Cluster Computing Workshops (CLUSTER Workshops 2024). DOI: 10.1109/CLUSTERWorkshops61563.2024.00015

-

Robert Schöne, Markus Velten, Daniel Hackenberg, Thomas Ilsche. "Energy Efficiency Features of the Intel Alder Lake Architecture". In: 15th ACM/SPEC International Conference on Performance Engineering (ICPE '24). DOI: 10.1145/3629526.3645040

-

Maximilian Sander, Hannes Tröpgen, Christian von Elm, Robert Schöne. "Towards Large-scale Top-Down Microarchitecture Analysis Using the Score-P Framework". In: Parallel Processing Workshops (Euro-Par 2024). (accepted for publication)

-

Lukas Alt, Anara Kozhokanova, Thomas Ilsche, Christian Terboven, Matthias S Müller. "An Experimental Setup to Evaluate RAPL Energy Counters for Heterogeneous Memory". In: 15th ACM/SPEC International Conference on Performance Engineering (ICPE '24). DOI: 10.1145/3629526.3645052

-

Jonas H. Müller Korndörfer, Ahmed Eleliemy, Osman Seckin Simsek, Thomas Ilsche, Robert Schöne, Florina M. Ciorba. "How Do OS and Application Schedulers Interact? An Investigation with Multithreaded Applications". In: 29th International Conference on Parallel and Distributed Computing (Euro-Par 2023). DOI: 10.1007/978-3-031-39698-4_15

-

Hannes Tröpgen, Mario Bielert, Thomas Ilsche. "Evaluating the Energy Measurements of the IBM POWER9 On-Chip Controller". In: ACM/SPEC International Conference on Performance Engineering (ICPE '23). DOI: 10.1145/3578244.3583729

-

Thomas Ilsche, Mario Bielert, Christian von Elm. "Bridging the Gap between Application Performance Analysis and System Monitoring" In: International Conference on Cluster Computing (CLUSTER '22). DOI: 10.1109/CLUSTER51413.2022.00080

-

Markus Velten, Robert Schöne, Thomas Ilsche, Daniel Hackenberg, "Memory Performance of AMD EPYC Rome and Intel Cascade Lake SP Server Processors". In:

International Conference on Performance Engineering (ICPE '22). DOI: 10.1145/3489525.3511689 -

Christian von Elm, Thomas Ilsche, Robert Schöne, Mario Bielert, Markus Schmidl. "Investigating the Cause and Effect of an AMD Zen Energy Management Anomaly". In: Companion of the ACM/SPEC International Conference on Performance Engineering (ICPE '21). DOI: 10.1145/3447545.3451193

-

Robert Schöne, Thomas Ilsche, Mario Bielert, Markus Velten, Markus Schmidl, Daniel Hackenberg. "Energy Efficiency Aspects of the AMD Zen 2 Architecture". In: Energy Efficient HPC State of the Practice Workshop (in conjunction with IEEE Cluster 2021). DOI: 10.1109/Cluster48925.2021.00087

-

Robert Schöne, Markus Schmidl, Mario Bielert, Daniel Hackenberg. "FIRESTARTER 2: Dynamic Code Generation for Processor Stress Tests". In: Energy Efficient HPC State of the Practice Workshop (in conjunction with IEEE Cluster). 2021. DOI: 10.1109/Cluster48925.2021.00084

-

Andreas Gocht, Robert Schöne, Mario Bielert, "Q-Learning Inspired Self-Tuning for Energy Efficiency in HPC" In: International Conference on High Performance Computing & Simulation (HPCS), 2019. DOI: 10.1109/HPCS48598.2019.9188112

-

Thomas Ilsche, Daniel Hackenberg, Robert Schöne, Mario Bielert, Franz Höpfner and Wolfgang E. Nagel. "MetricQ: A Scalable Infrastructure for Processing High-Resolution Time Series Data" In: 2019 IEEE/ACM Industry/University Joint International Workshop on Data-center Automation, Analytics, and Control (DAAC). 2019. DOI: 10.1109/DAAC49578.2019.00007

- Robert Schöne, Thomas Ilsche, Mario Bielert, Andreas Gocht, Daniel Hackenberg. "Energy Efficiency Features of the Intel Skylake-SP Processor and Their Impact on Performance" In: 6th Special Session on High Performance Computing Benchmarking and Optimization (HPBench). 2019. DOI: 10.1109/HPCS48598.2019.9188239

-

Daniel Molka, Robert Schöne, Daniel Hackenberg, Wolfgang E. Nagel. "Detecting Memory-Boundedness with Hardware Performance Counters", In: International Conference on Performance Engineering (ICPE), 2017. DOI: 10.1145/3030207.3030223

-

Thomas Ilsche, Robert Schöne, Joseph Schuchart, Daniel Hackenberg, Marc Simon, Yiannis Georgiou and Wolfgang E. Nagel. "Power Measurement Techniques for Energy-Efficient Computing: Reconciling Scalability, Resolution, and Accuracy" In: Second Workshop on Energy-Aware High Performance Computing (EnA-HPC). 2017. DOI: 10.1007/s00450-018-0392-9

- Thomas Ilsche, Robert Schöne, Mario Bielert, Andreas Gocht and Daniel Hackenberg. "lo2s – Multi-Core System and Application Performance Analysis for Linux" In: Workshop on Monitoring and Analysis for High Performance Computing Systems Plus Applications (HPCMASPA). 2017. DOI: 10.1109/CLUSTER.2017.116

- Thomas Ilsche, Marcus Hähnel, Robert Schöne, Mario Bielert and Daniel Hackenberg. "Powernightmares: The Challenge of Efficiently Using Sleep States on Multi-Core Systems" In: 5th Workshop on Runtime and Operating Systems for the Many-core Era (ROME). 2017. https://doi.org/10.1007/978-3-319-75178-8_50

- Robert Schöne, Thomas Ilsche, Mario Bielert, Daniel Molka, Daniel Hackenberg. "Software Controlled Clock Modulation for Energy Efficiency Optimization on Intel Processors" In: 4th International Workshop on Energy Efficient Supercomputing (E2SC). 2016. DOI: doi.org/10.1109/E2SC.2016.015

-

Joseph Schuchart, Daniel Hackenberg, Robert Schöne, Thomas Ilsche, Ramkumar Nagappan, Michael K. Patterson. “The Shift from Processor Power Consumption to Performance Variations: Fundamental Implications at Scale” In: First Workshop on Energy-Aware High Performance Computing (EnA-HPC). 2016. DOI: 10.1007/s00450-016-0327-2

-

R. Schöne, R. Tschüter, T. Ilsche, J. Schuchart, D. Hackenberg, and W. E. Nagel. “Extending the Functionality of Score-P through Plugins: Interfaces and Use Cases” In: Tools for High Performance Computing 2016, DOI: 10.1007/978-3-319-56702-0_4

- Mario Bielert, Florina M. Ciorba, Kim Feldhoff, Thomas Ilsche, and Wolfgang E. Nagel. “HAEC-SIM: A Simulation Framework for Highly Adaptive Energy-Efficient Computing Platforms.” In: Eighth Conference on Simulation Tools and Techniques. 2015. DOI: 10.4108/eai.24-8-2015.2261105

- Daniel Hackenberg, Robert Schöne, Thomas Ilsche, Daniel Molka, Joseph Schuchart, and Robin Geyer: " An Energy Efficiency Feature Survey of the Intel Haswell Processor" In: 2015 IEEE International Parallel and Distributed Processing Symposium Workshop (IPDPSW). DOI: 10.1109/IPDPSW.2015.70

- Thomas Ilsche, Daniel Hackenberg, Stefan Graul, Joseph Schuchart, and Robert Schöne. “Power Measurements for Compute Nodes: Improving Sampling Rates, Granularity, and Accuracy” In: Sixth International Green Computing Conference and Sustainable Computing Conference (IGSC). 2015. DOI: 10.1109/IGCC.2015.7393710

- Daniel Molka, Daniel Hackenberg, Robert Schöne, Wolfgang E. Nagel “Cache Coherence Protocol and Memory Performance of the Intel Haswell-EP Architecture”, Proceedings of the 44th International Conference on Parallel Processing (ICPP'15), IEEE, 2015

- Daniel Hackenberg, Thomas Ilsche, Joseph Schuchart, Robert Schöne, Wolfgang E. Nagel, Marc Simon, and Yiannis Georgiou. HDEEM: High Definition Energy Efficiency Monitoring. In: Proceedings of the 2nd International Workshop on Energy Efficient Supercomputing (E2SC). 2014. DOI: 10.1109/E2SC.2014.13

- Daniel Molka, Daniel Hackenberg, Robert Schöne, “Main Memory and Cache Performance of Intel Sandy Bridge and AMD Bulldozer”, In Proceedings of the 2014 ACM SIGPLAN workshop on Memory Systems Performance and Correctness (MSPC'14), ACM, 2014

- D. Hackenberg, T. Ilsche, R. Schoene, D. Molka, M. Schmidt, and W. E. Nagel: Power Measurement Techniques on Standard Compute Nodes: A Quantitative Comparison. In IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS13), Austin, TX USA, April 21-23, 2013.

- R. Schöne, D. Hackenberg, D. Molka, “Memory performance at reduced CPU clock speeds: an analysis of current x86_64 processors”, In Proceedings of the 2012 USENIX conference on Power-Aware Computing and Systems (HotPower'12), October 7, 2012, Hollywood, USA

- R. Schöne, D. Hackenberg, D. Molka, “Simultaneous Multithreading on x86_64 Systems: An Energy Efficiency Evaluation”, In Procedings of the 4th Workshop on Power-Aware Computing and Systems (HotPower'11), October 23-26, 2011, Cascais, Portugal

- D. Molka, R. Schöne, D. Hackenberg, M. S. Müller, “Memory Performance and SPEC OpenMP Scalability on Quad-Socket x86 64 Systems”, In Procedings of the 11th International Conference on Algorithms and Architectures for Parallel Processing (ICA3PP'11), October 24-26 2011, Melbourne, Australia

- D. Molka, D. Hackenberg, R. Schöne and M. S. Müller, “Characterizing the Energy Consumption of Data Transfers and Arithmetic Operations on x86-64 Processors”, In Proceedings of the 1st International Green Computing Conference (IGCC'10), pages 123-133, IEEE, 2010

- D. Hackenberg, D. Molka and W. E. Nagel, “Comparing Cache Architectures and Coherency Protocols on x86-64 Multicore SMP Systems”, In Proceedings of the 42nd International Symposium on Microarchitecture (MICRO'09), pages 413-422, ACM, 2009

- D. Molka, D. Hackenberg, R. Schöne and M. S. Müller, “Memory Performance and Cache Coherency Effects on an Intel Nehalem Multiprocessor System”, In Proceedings of the 18th International Conference on Parallel Architectures and Compilation Techniques (PACT'09), pages 261-270, IEEE, 2009

- Daniel Hackenberg, Robert Schöne, Wolfgang E Nagel, Stefan Pflüger, Optimizing OpenMP parallelized DGEMM calls on SGI Altix 3700, Lecture Notes in Computer Science for Euro-Par 2006 Parallel Processing, pages 145-154, Januar 01 2006, http://dx.doi.org/10.1007/11823285_15

- Guido Juckeland, Michael Kluge, Wolfgang E. Nagel and Stefan Pflüger, Performance analysis with BenchIT: portable, flexible, easy to use, in: 1st International Conference on Quantitative Evaluation of Systems (QEST 2004), Proceedings, pages 320--321, IEEE Computer Society, 2004